10课程设计收尾及优秀作品展示答辩【FPGA模型机课程设计】

- 前言

- 说明

- 推荐

- 10课程设计收尾及优秀作品展示答辩

- 安排

- 目录

- 一、单周期CPU的设计过程

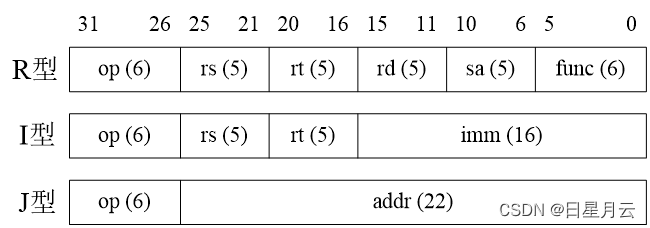

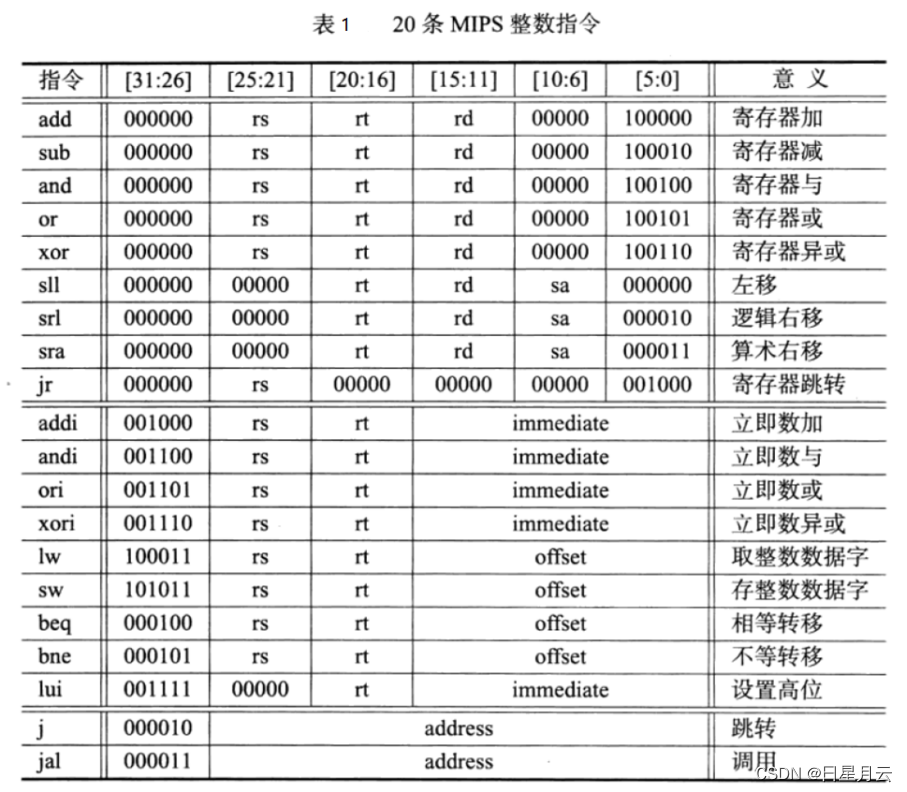

- 1、基本的20条指令

- 固定指令格式设计

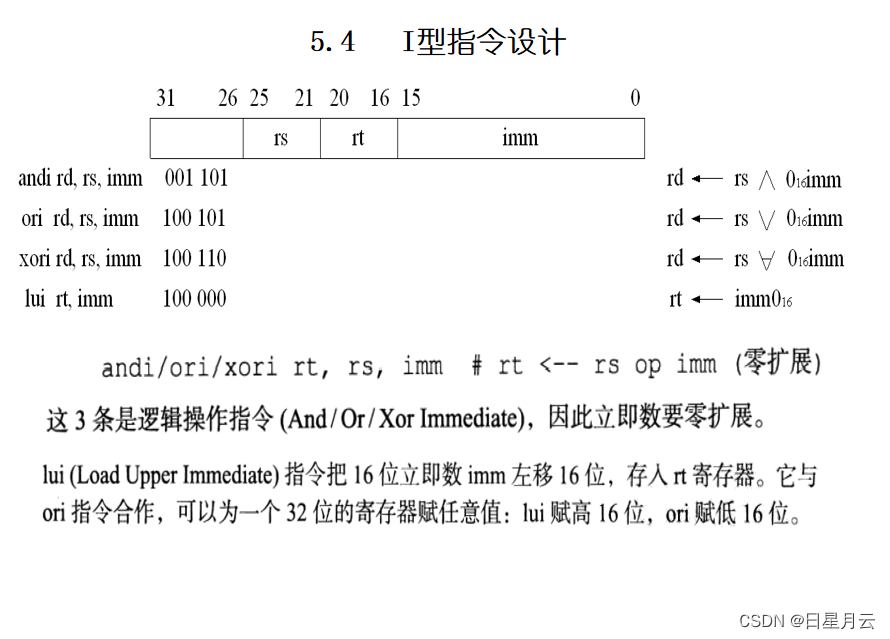

- I 型指令设计

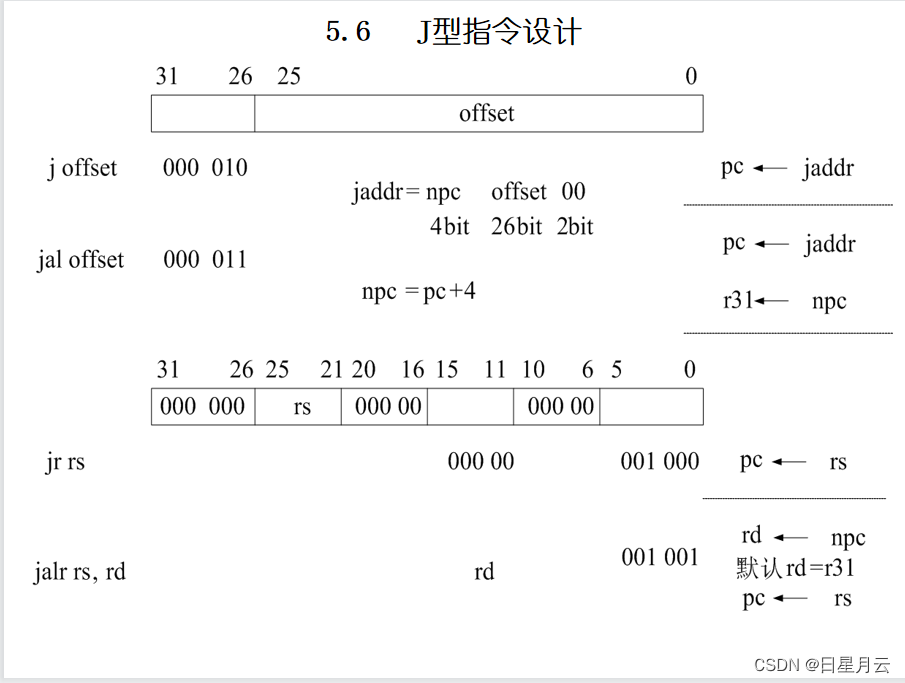

- J型指令设计

- lw sw指令设计

- 2、扩展的20条指令

- J型扩展指令设计

- 乘法除法指令格式

- 3、实现中断异常相关指令

- 原子指令设计

- 中断与异常相关指令

- 二、单周期CPU的下板过程

- 设计

- 实机测试

- 其余设计

- 三、流水CPU的设计

- MIPS的一种简单实现

- 五段流水线CPU通路基本构成

- 1 测试指令流水

- 2解决数据冲突

- ID的关于数据冲突的处理

- 附录

- 表1 20条MIPS整数指令

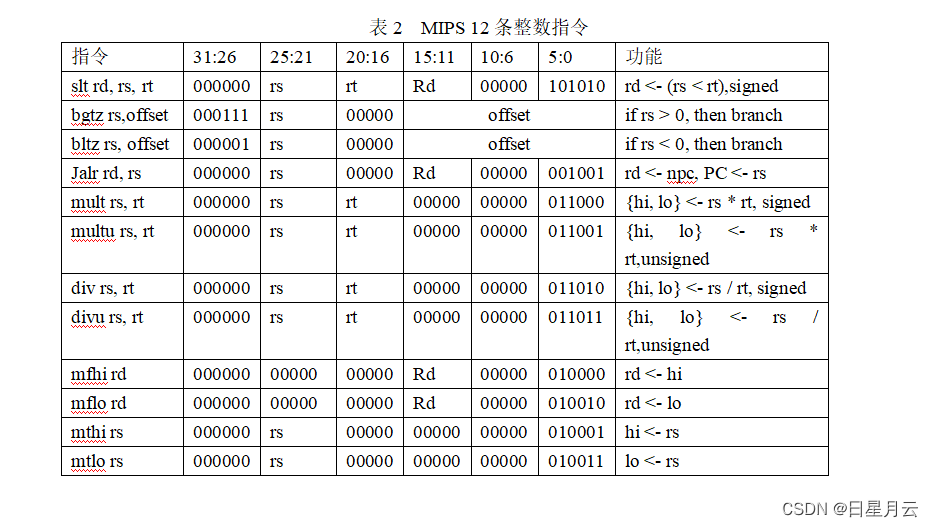

- 表2 MIPS 12条整数指令

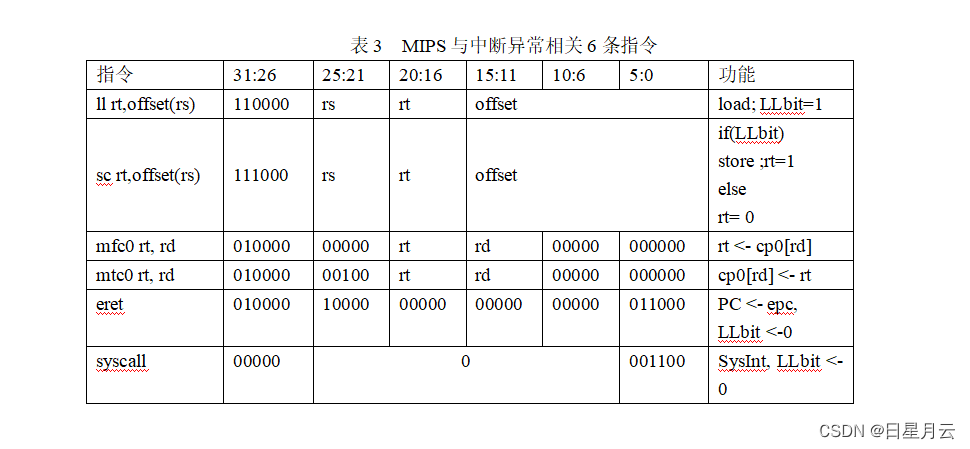

- 表3 MIPS 与中断异常相关6条指令

- 最后

前言

2023-6-1 17:10:46

答辩主要讲的是设计思路

代码测试可以看具体文章

以下内容源自《【FPGA模型机课程设计】》

仅供学习交流使用

小组:孤星独吟

所有资料均参考于老师的教学资料

所有代码均为自己手敲

所有内容均已发布到CSDN@日星月云

说明

答辩PPT中主要讲了设计框图

本来不准备配文字的

但是对于

- 1.3中断异常实现

- 3流水线CPU的设计

做了必要的代码贴图和文字说明

本篇博客做了详细的文字说明

代码测试与结果可以在其余博客中体现

本篇博客中其余的测试结果波形在推荐中的其余博客体现

现在设计到

- 单周期CPU中异常调用的功能不完善LLbit<-0,未给出相关测试

- 单周期下板√

- 流水线的WAR冲突解决√

- 流水线的Load相关有点问题

- 流水线延迟分支未实现

- 流水线中断异常未实现

推荐

0集中实践环节计划书【FPGA模型机课程设计】

5模型机整体的联调【FPGA模型机课程设计】

单周期-开发过程【FPGA模型机课程设计】

单周期CPU模型机下载-实机测试【FPGA模型机课程设计】

流水线-开发过程【FPGA模型机课程设计】

10课程设计收尾及优秀作品展示答辩

小组:孤星独吟

安排

第二周周五:

课程设计收尾及优秀作品展示答辩

学生小组在通过验收后,录制模型机演示视频(一般<3min),优秀设计者需制作答辩讲解ppt。模型机演示视频应包括:所设计的指令集、模型机架构、程序运行演示和对运行结果的说明;曾经出现的问题及解决办法;每位成员在设计开发团队中起到的作用。所录视频为mp4格式,要求屏幕视角大,图像清晰,声音洪亮,演示运行过程清楚明了,运行结果是否正确有解释说明。视频最好有字幕提示。

目录

- 01单周期CPU的设计

- 02.单周期CPU的下板

- 03.流水线CPU的设计

- 04.附录

重点:讲1.3异常中断设计与3流水线CPU的设计

一、单周期CPU的设计过程

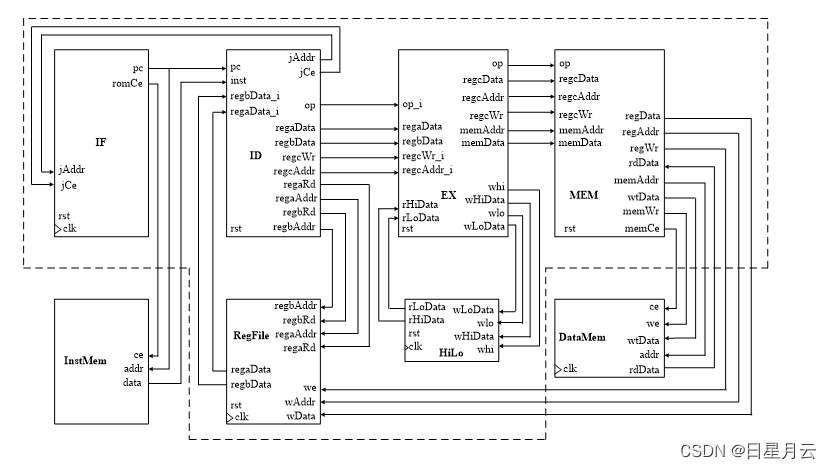

1、基本的20条指令

固定指令格式设计

定长指令

操作码+操作数

I 型指令设计

操作码+源地址+目的地址+立即数

目的数据=源数据 op 立即数(扩展)

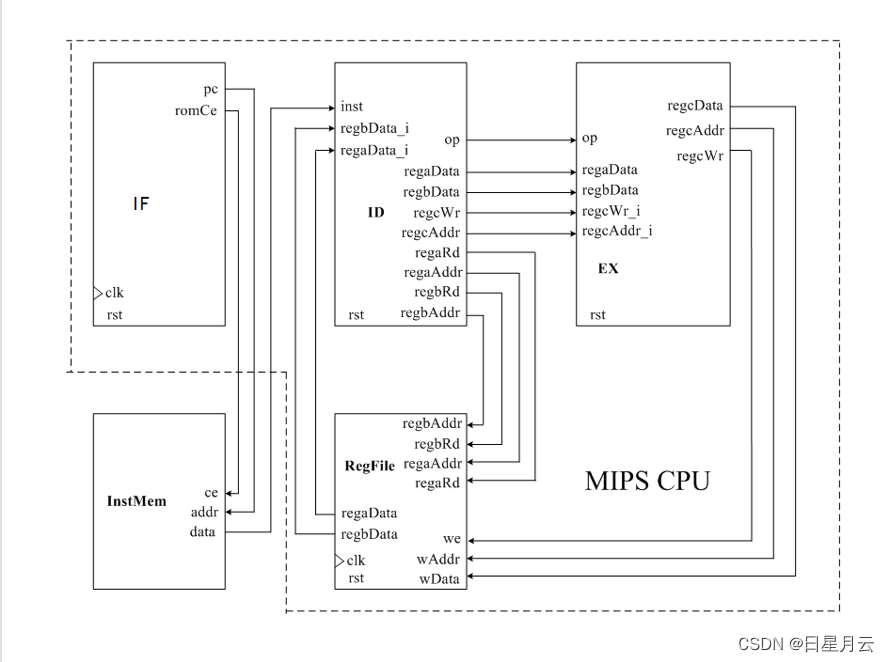

IF取指:

- 输入 clk rst

- 操作

pc=0和romCe=无效(复位有效)

pc+=4和romCe=有效 - 输出 romCe 片选信号和pc

InstMem指令存储器:

- 输入 ce addr

- 内部存储 reg [31:0] instmem [1023 : 0];

- 输出 data = instmem[addr[11 : 2]];

ID译码:

- 输入 rst和inst和regaData_i regbData_i

- 操作

通过对op的判断I指令和R型指令

准备数据regaData(从regaData_i和imm中二选一)、regbData、regcWr、regcAddr - 输出 op regaRd regaAddr regbRd regbAddr

RegFile寄存器文件:

- 输入 clk rst和regaRd regaAddr regbRd regbAddr和we wAddr wData

- 内部存储 reg [31:0] reg32 [31 : 0];

- 操作

- 读regaData = reg32[regaAddr] regbData = reg32[regbAddr];

- 写reg32[waddr] = wdata;

- 输出 regaData regbData

EX执行

- 输入 op regaData regbData、regcWr_i、regcAddr_i

- 操作

regcData=regaData (op) regbData - 输出regcData regcAddr regcWr

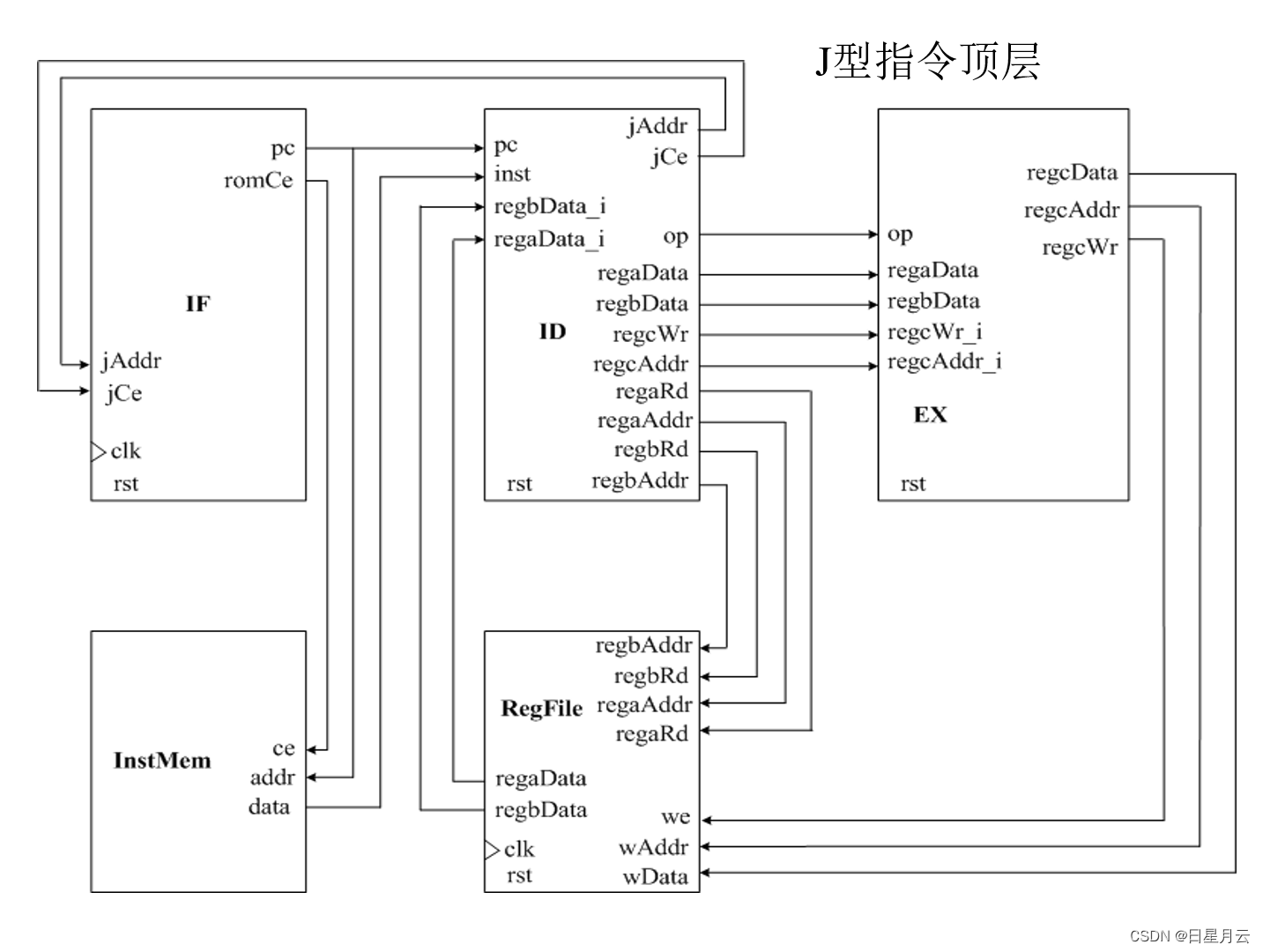

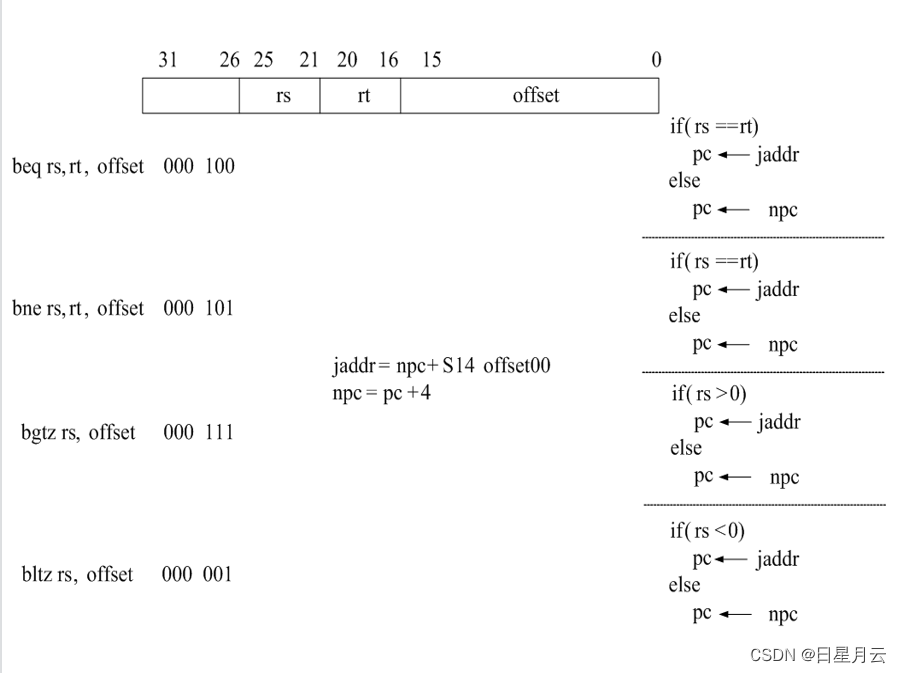

J型指令设计

IF

- 输入 jAddr jCe

操作 如果jCe有效,pc=jAddr

ID

- 操作

如果是j型指令,jCe有效,jAddr=跳转地址 - 输出 jAddr jCe

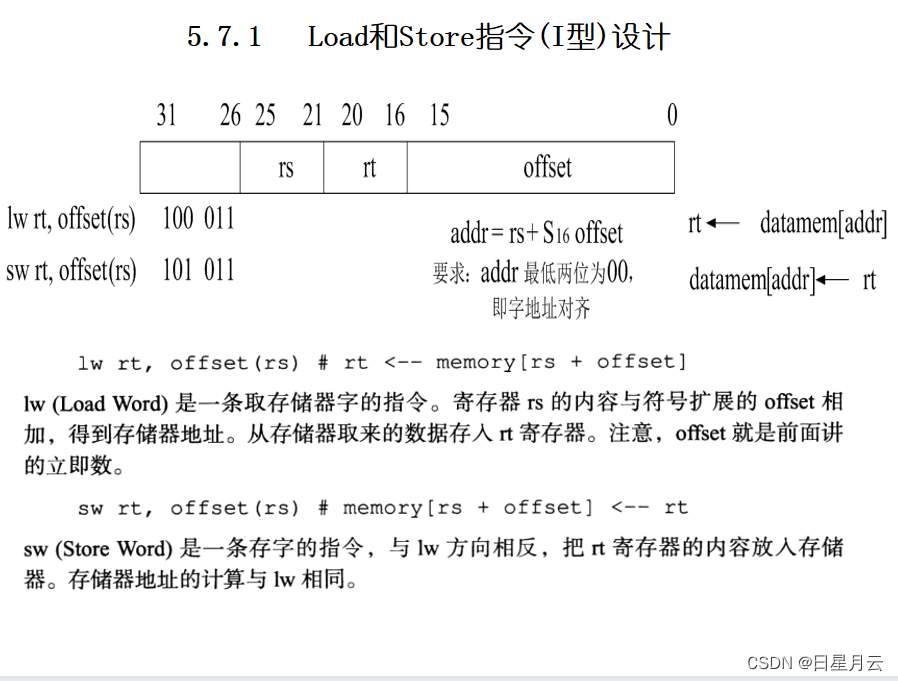

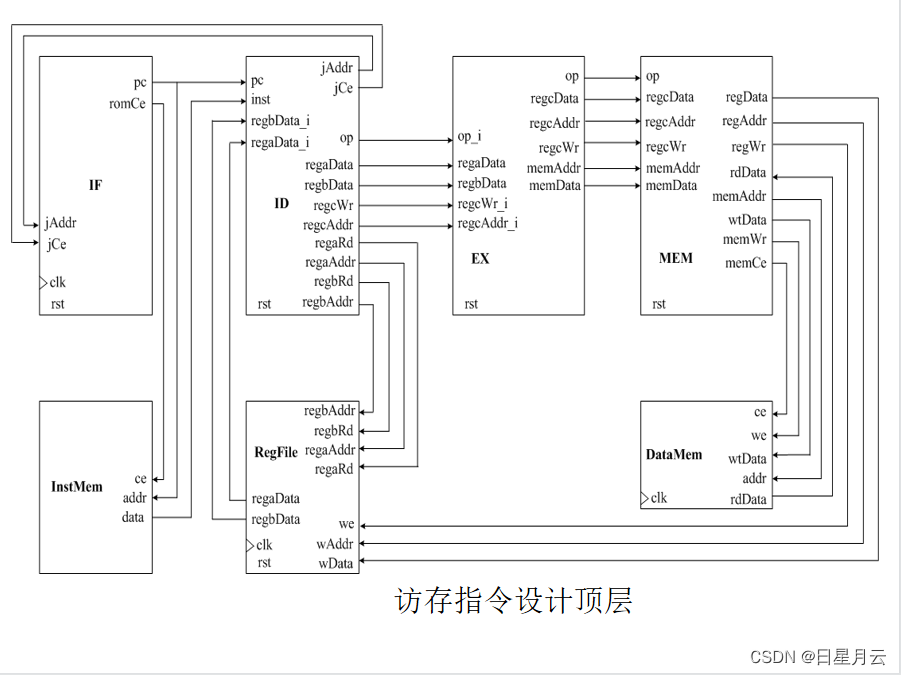

lw sw指令设计

ID译码

- 操作

如果指令是访存指令,regaData = regaData_i + imm;

EX执行

- 操作

memAddr=regaData

memData=regbData - 输出:memAddr memData

MEM访存:

- 输入op regcData regcAdd rregcWr memAddr memData和rdData

- 操作

- lwwtData = `Zero;memWr = `RamUnWrite; memCe = `RamEnable; - swwtData = memData memWr = `RamWritememCe = `RamEnable

- 输出 regData regAddr regWr和memAddr wtData memWr memCe

DataMem访存:

- 输入:clk和ce we wtData addr

内部存储: reg [31:0] datamem [1023 : 0]; - 操作:

读rdData = datamem[addr[11 : 2]];

写datamem[addr[11 : 2]] = wtData; - 输出 rdData

2、扩展的20条指令

J型扩展指令设计

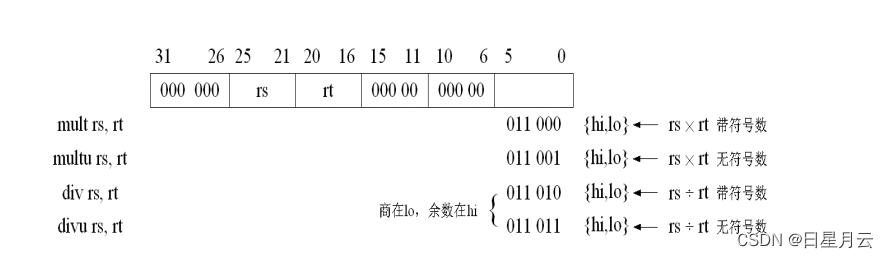

乘法除法指令格式

ID译码:

- 准备乘除的操作数

EX执行:

- 输入:rHiData和rLoData

- 操作

Hi:高位或余数

Lo:低位或商 - 输出 whi wHiData wlo wLoData

HiLo寄存器

- 操作

内部存储reg [31:0]hi,lo;

读写HiLo寄存器

增加HiLo寄存器

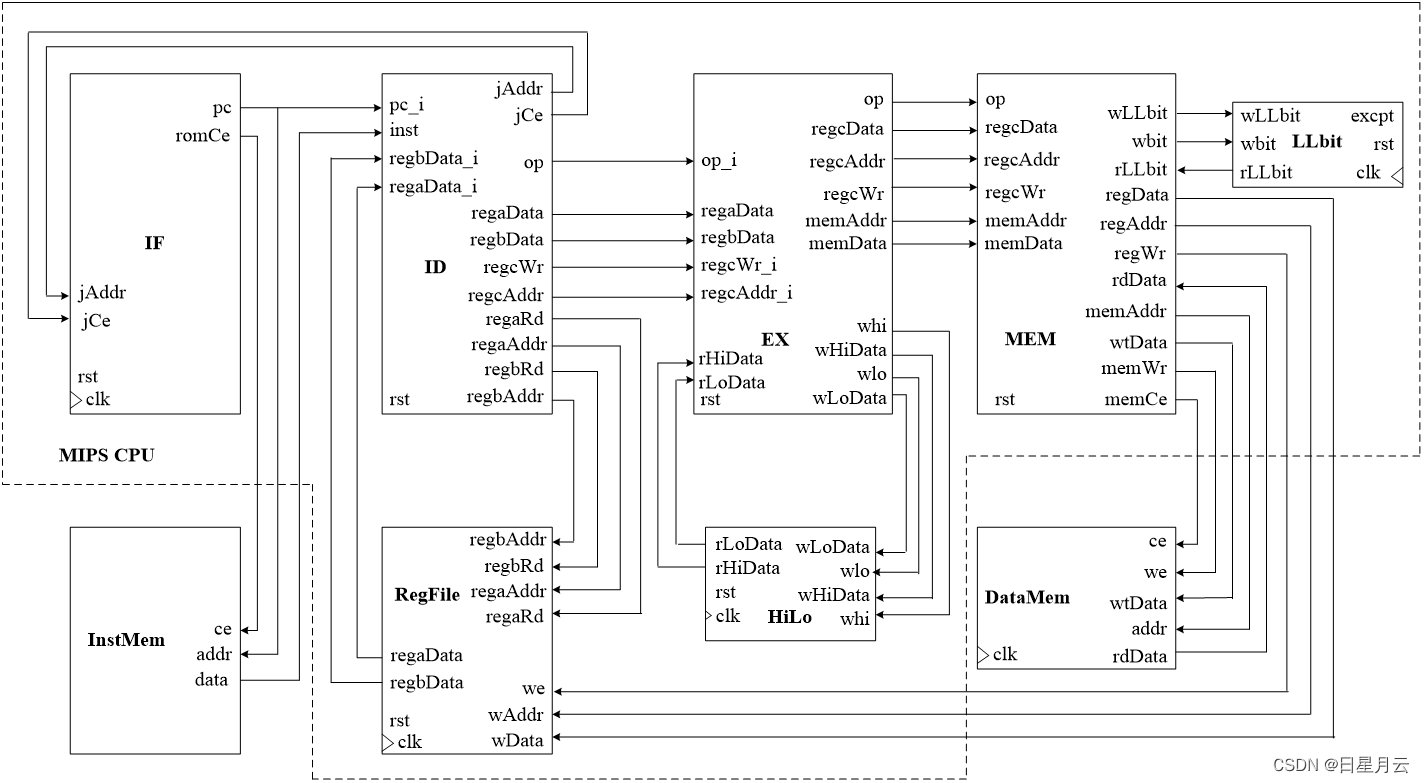

3、实现中断异常相关指令

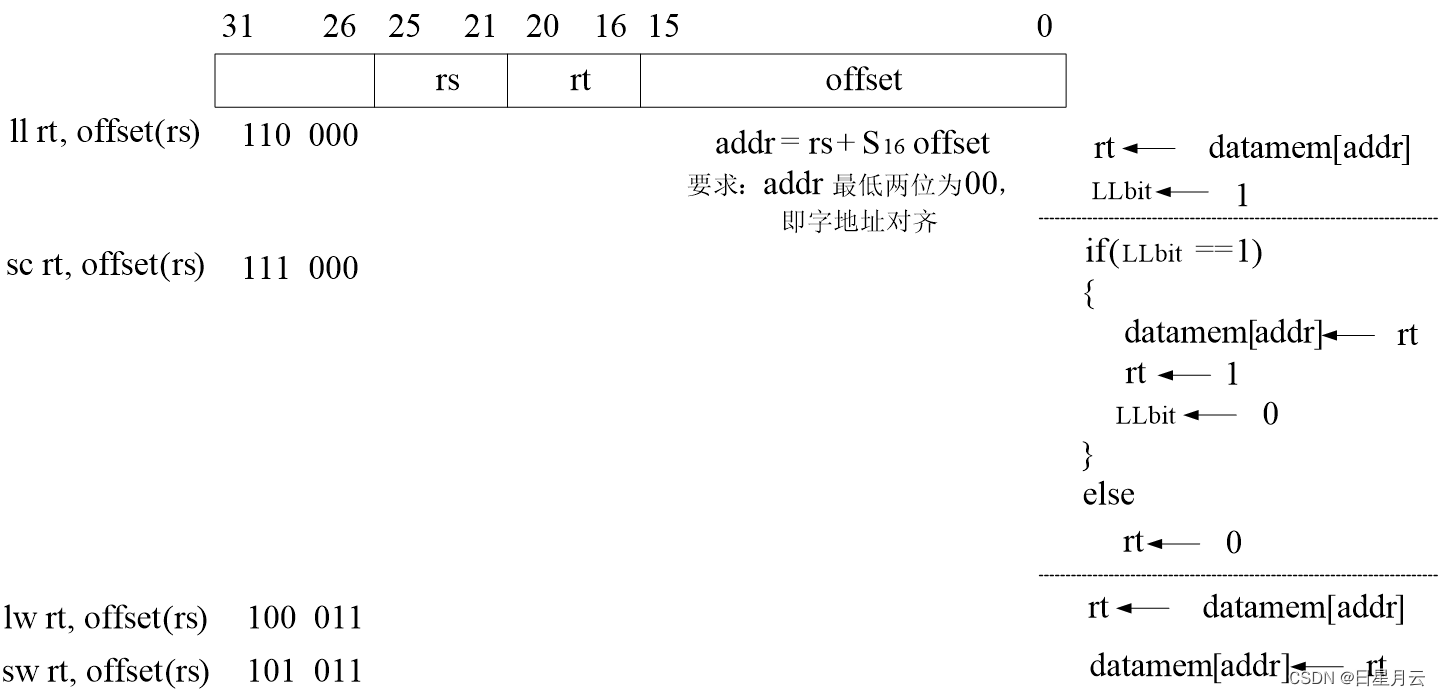

原子指令设计

ID

- 准备数据

MEM

- 操作:

- LL:

rt <-datamem[addr]

LLbit<-1 - SC:

if(LLbit ==1){

datamem[addr]<-rt

rt<-1

LLbit<-0}

else

rt<-0

- LL:

LLbit寄存器

- 操作

内部存储reg LLbit;

读写LLbit值

增加了LLbit

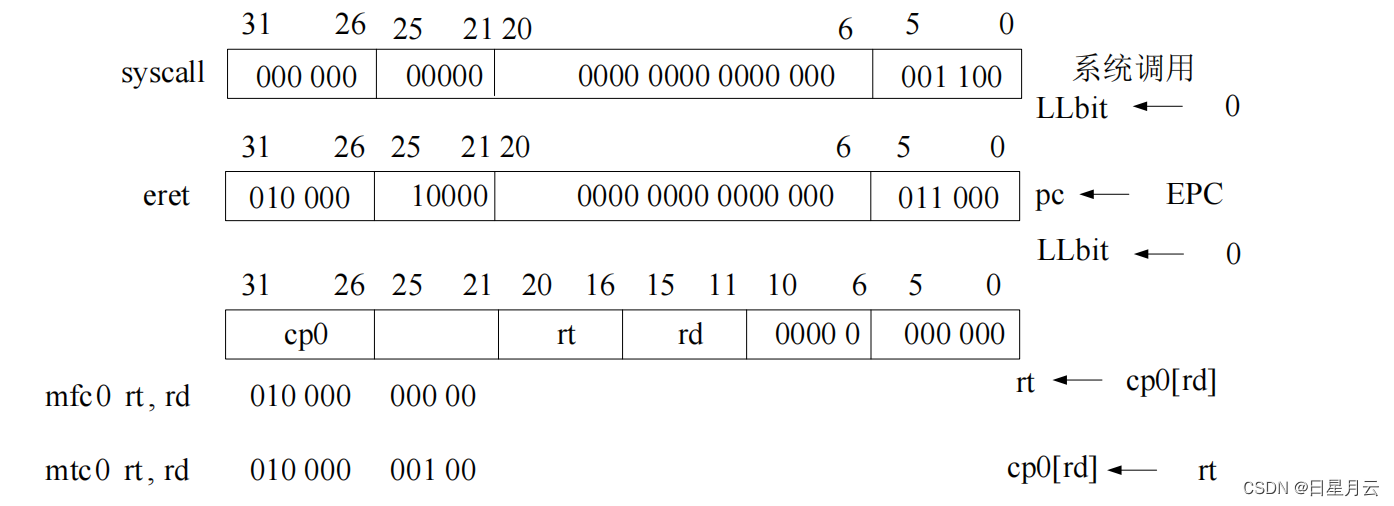

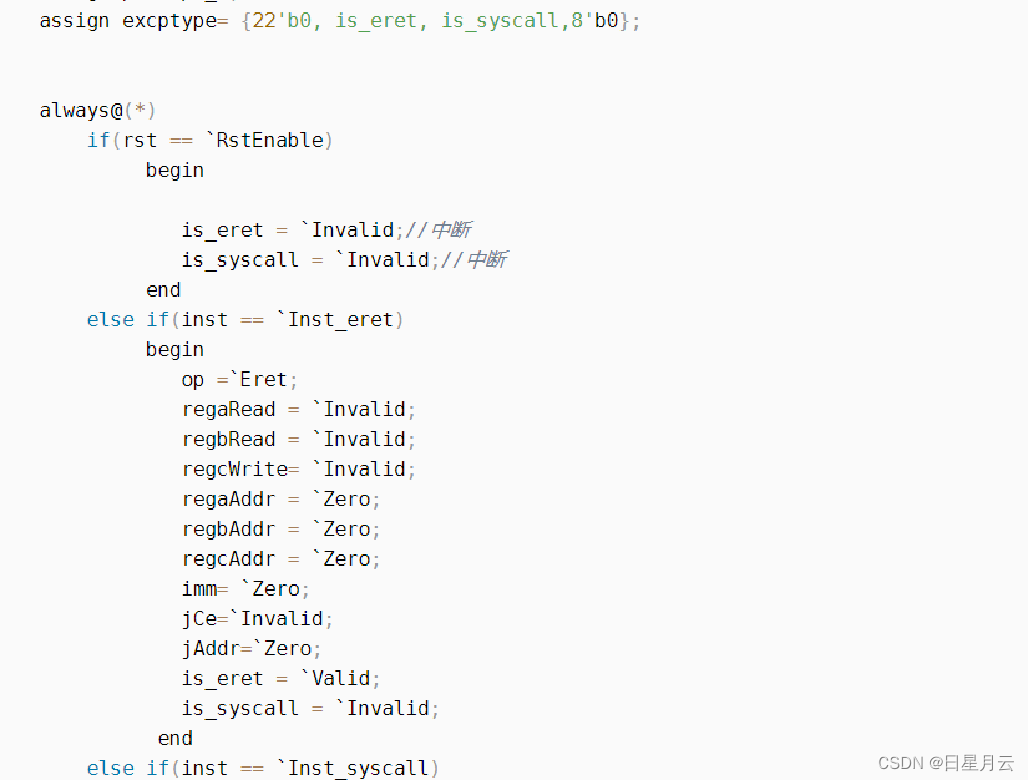

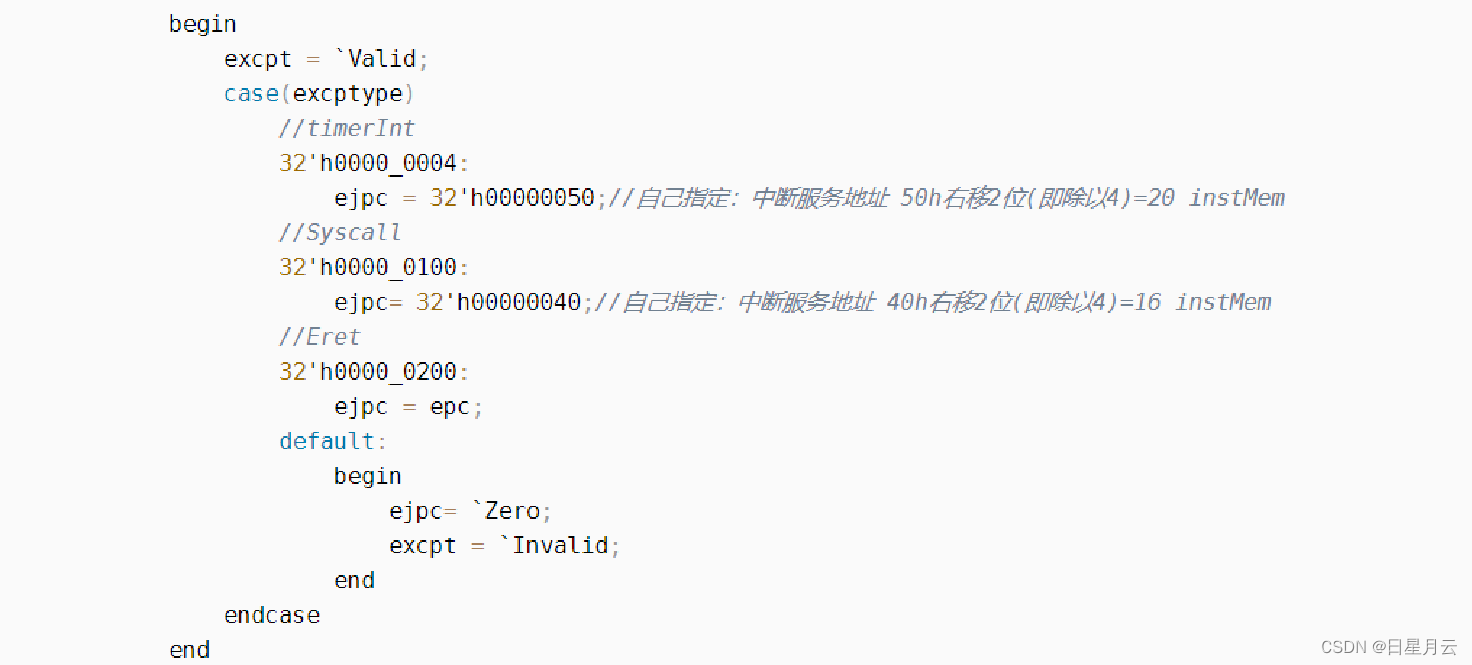

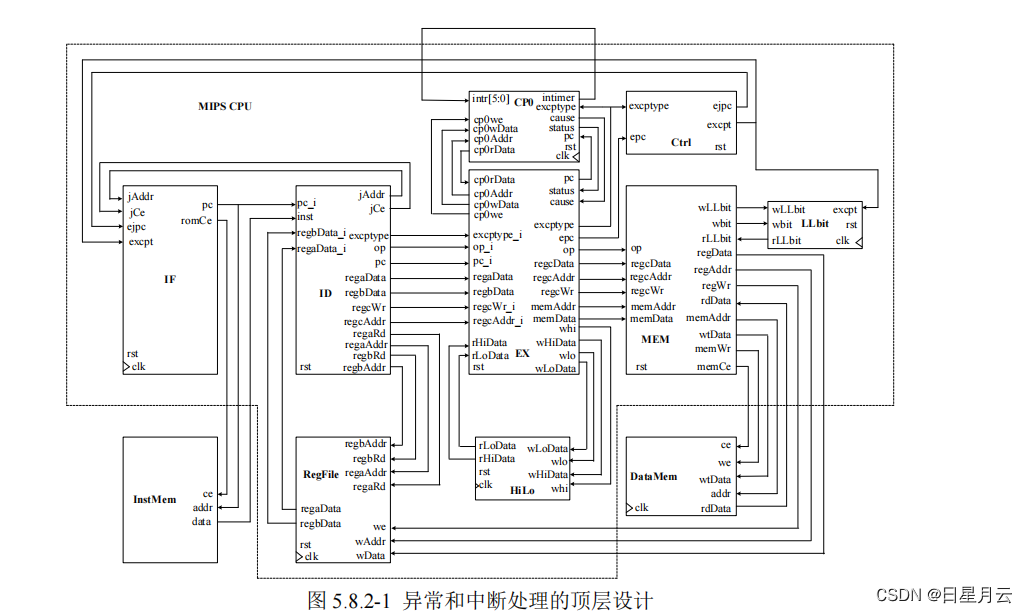

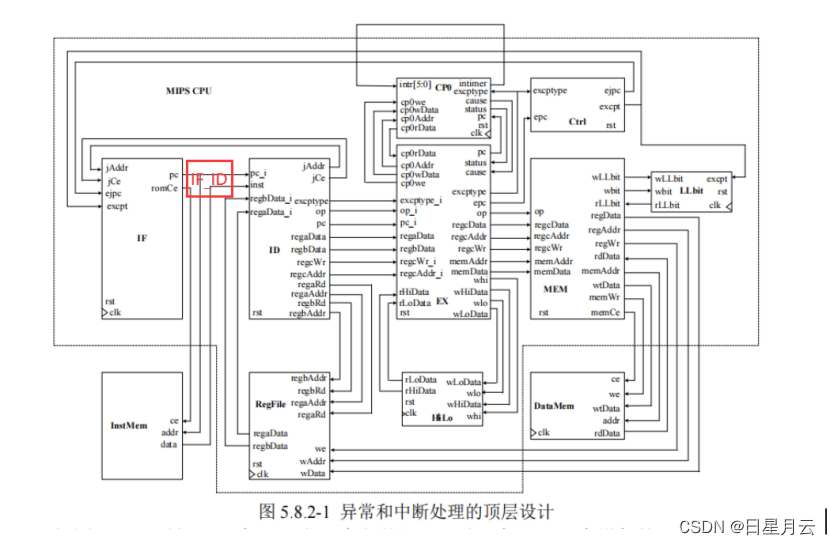

中断与异常相关指令

全译码 二次译码

异常或中断处理过程如下:

(1)ID 模块根据译码结果,

通过 excptype 收集 Syscall 和 Eret 指令,检测是否有对应的异常发生。

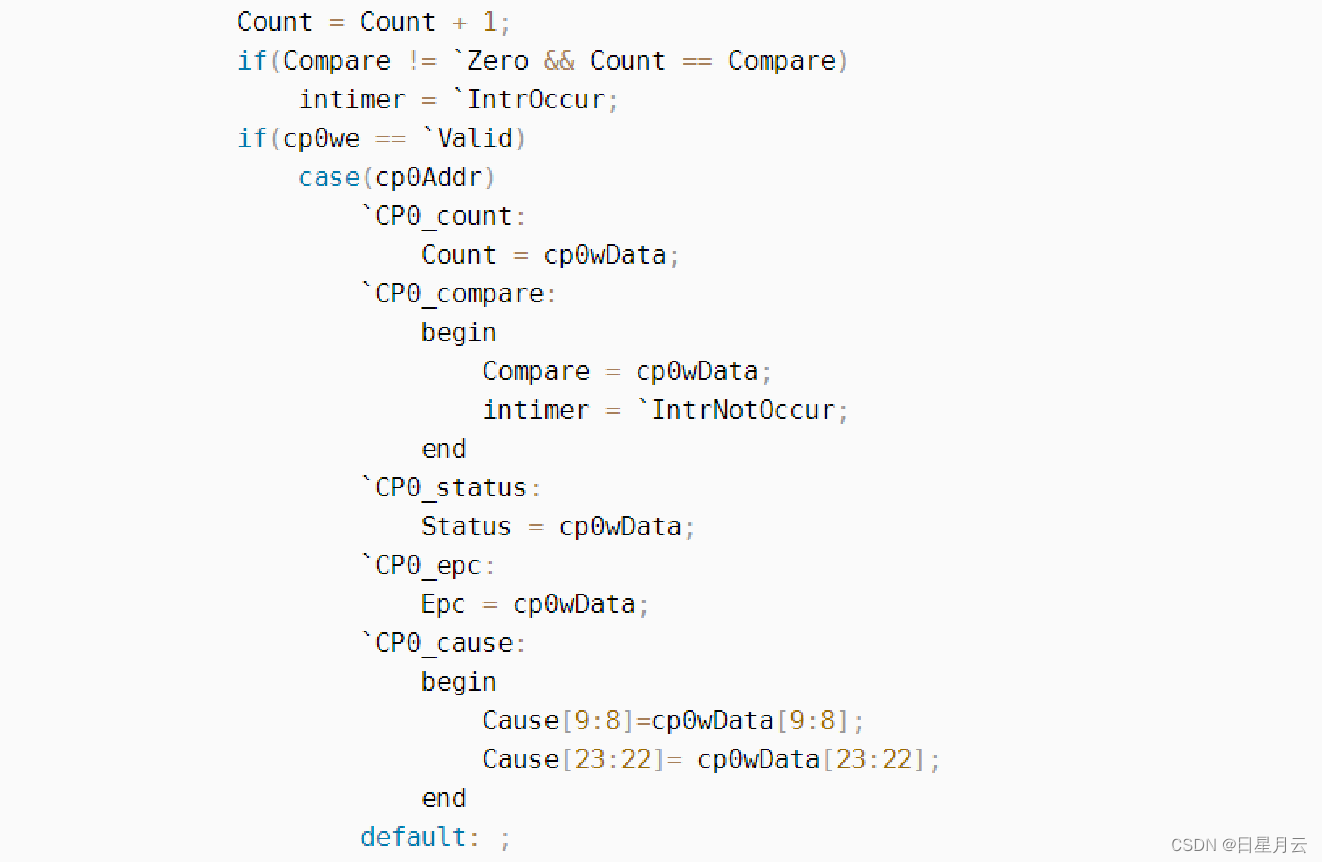

协处理器CP0模块

中断设置

读写CP0寄存器

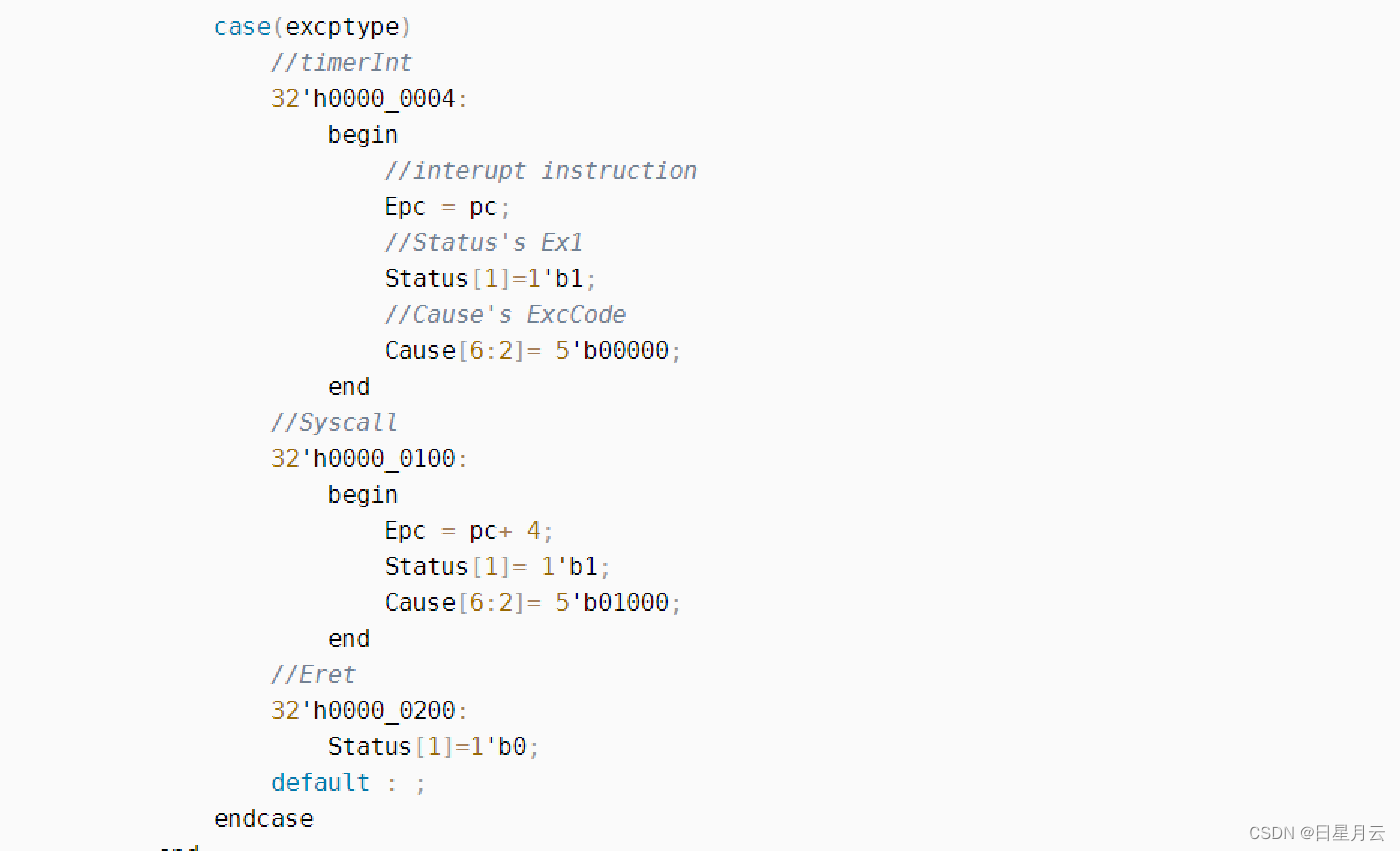

控制Ctrl模块

主要是在查询方式下,提供异常或中断服务程序的首地址。

IF

- 输入:ejpc excpt

- 操作:pc=ejpc

ID:

- 操作

首先判断是不是中断与异常相关指令 - 输出 ID给EX传送异常类型excptype

EX

在代码设计中,选用Cause寄存器的IP[2]对应的0号硬件中断,即定时中断intimer输出到IP[2]上,然后在执行EX模块检测IP[2]这位是否为1,并且是否允许中断,从而确定定时中断是否有效。若异常或中断有效,则当前指令不会被继续执行,后面的操作都设为无效。

CP0

读写5个寄存器

Ctrl

控制Ctrl模块为新增加模块,主要是在查询方式下,提供异常或中断服务程序的首地址。

增加CP0与Ctrl模块

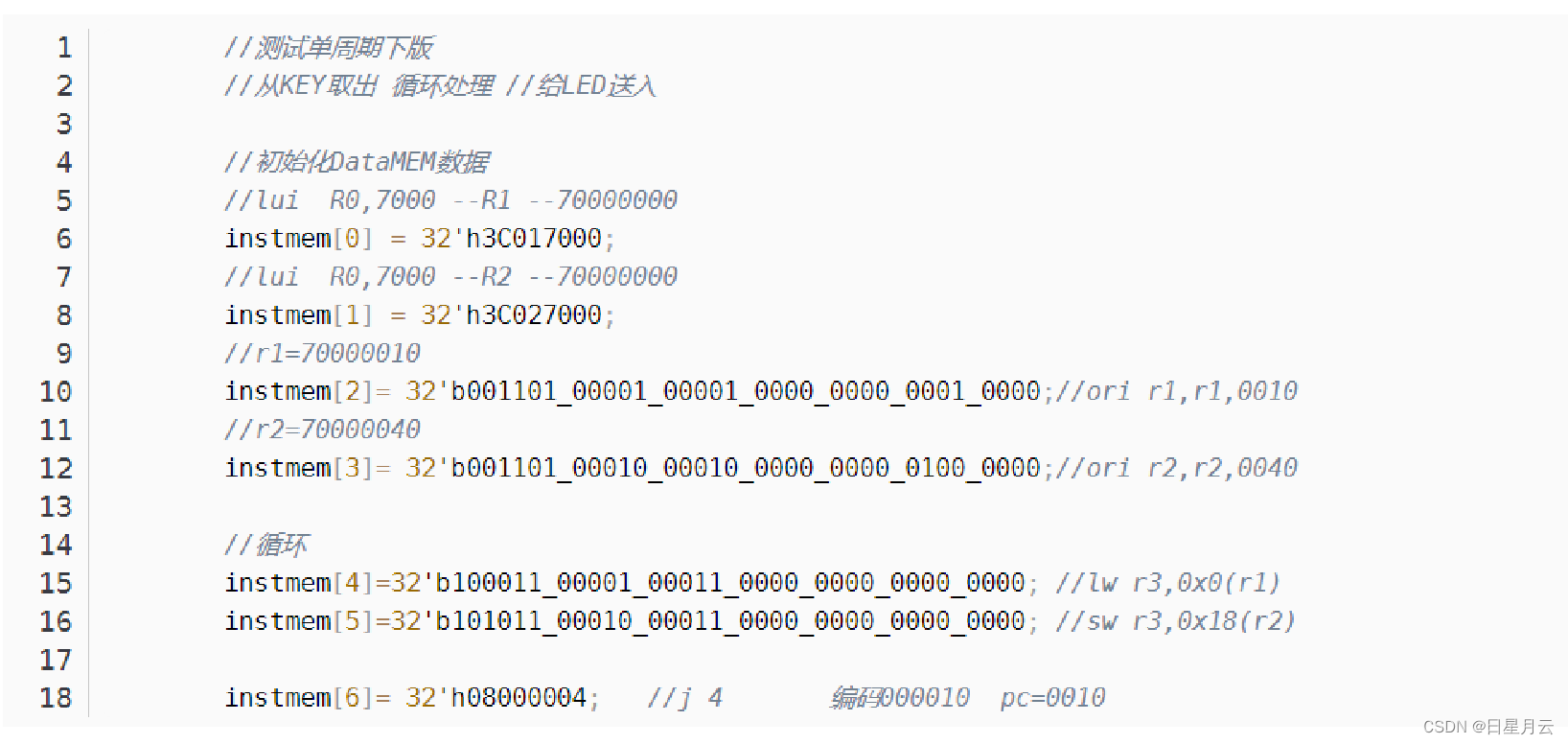

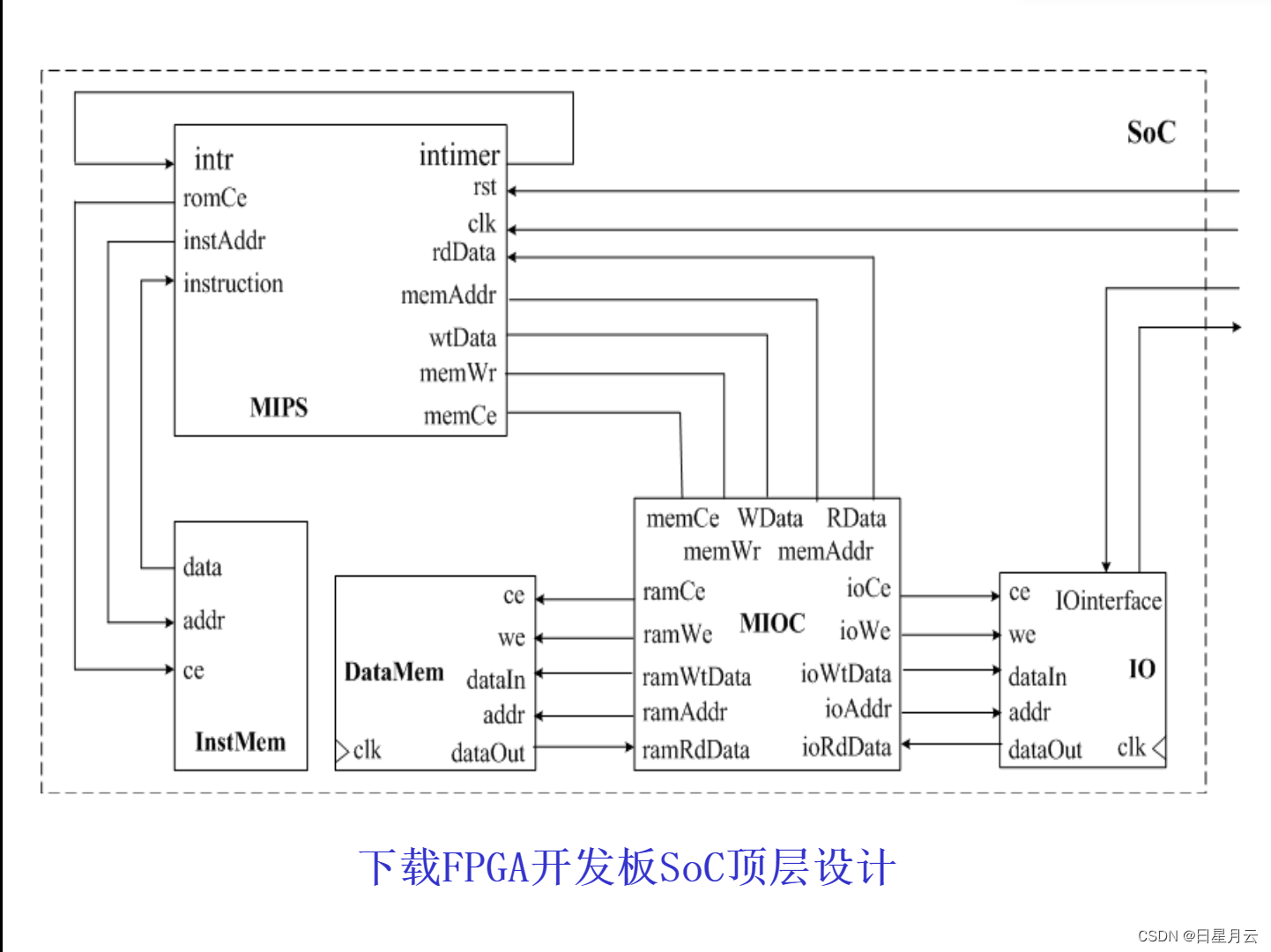

二、单周期CPU的下板过程

设计

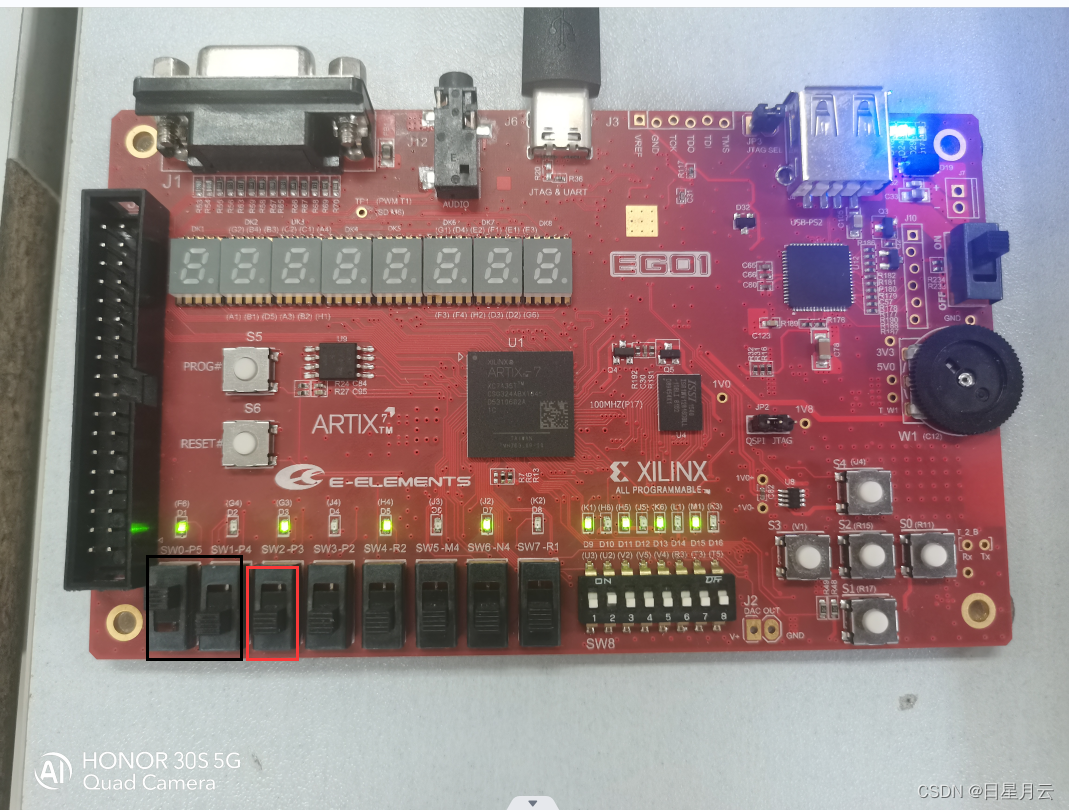

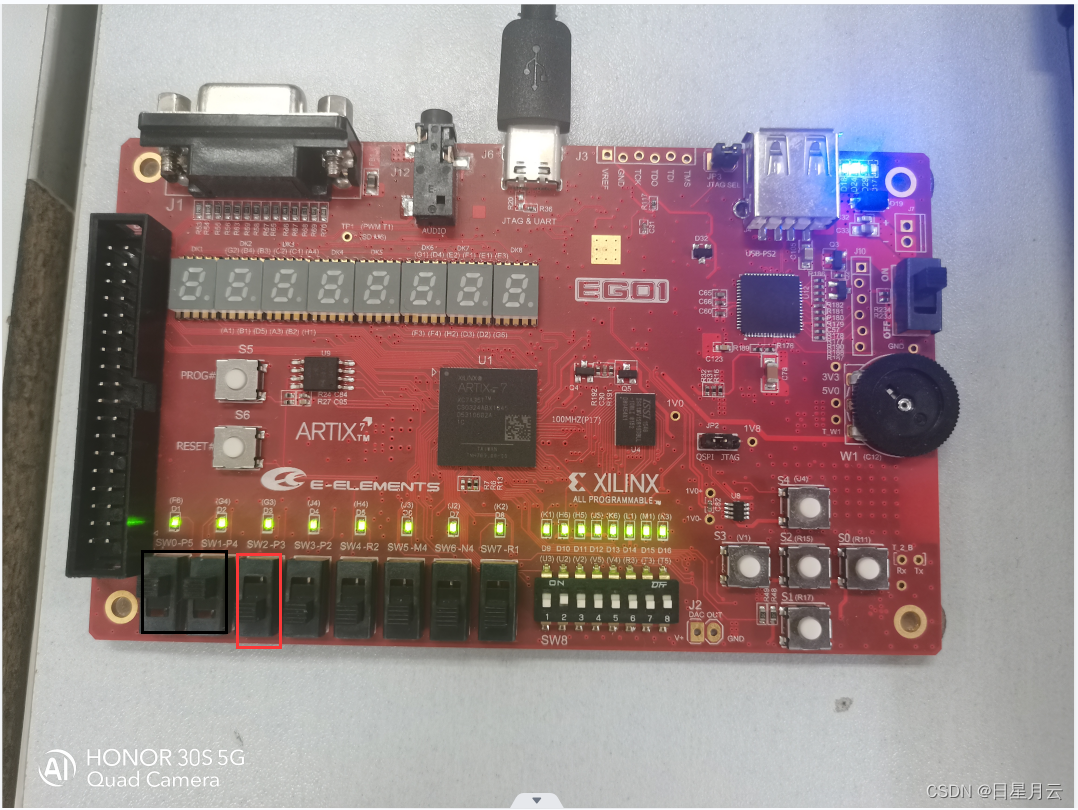

实机测试

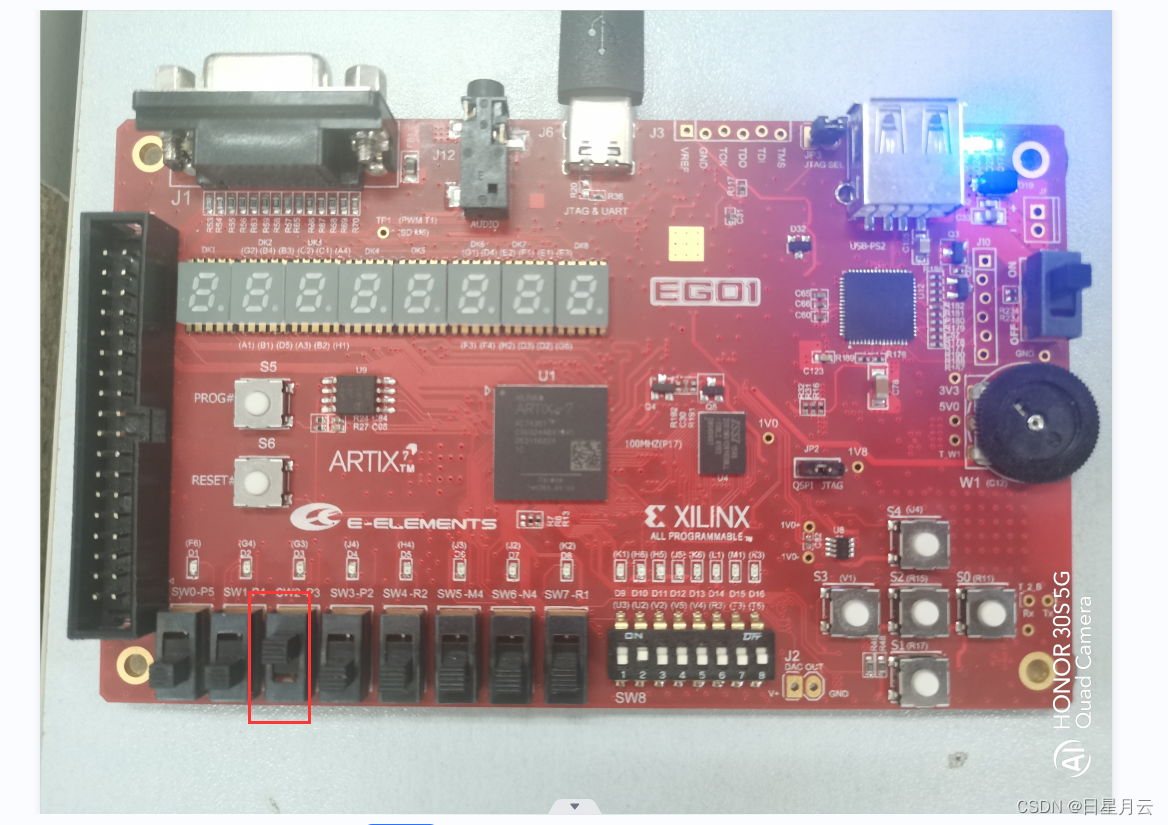

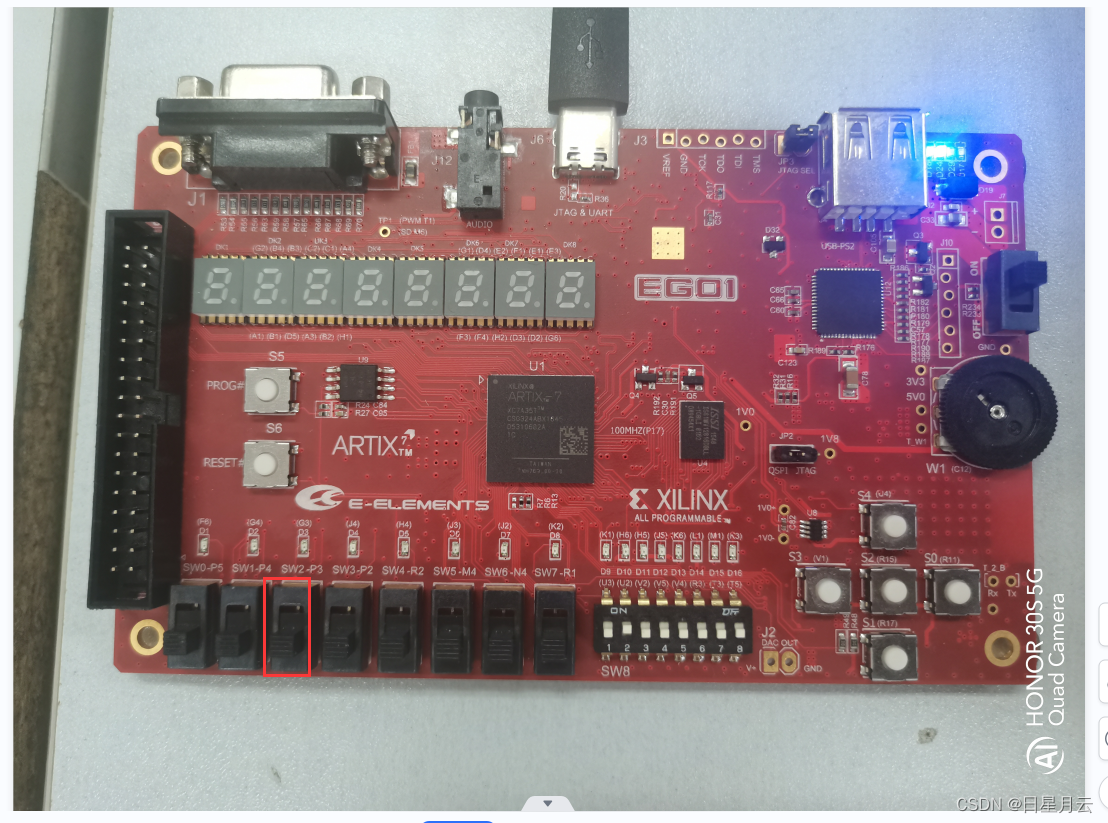

首先,需要把rst值置为有效

在约束文件中

可以看到rst连接的是P3

也就是SW2

之后把rst置为无效

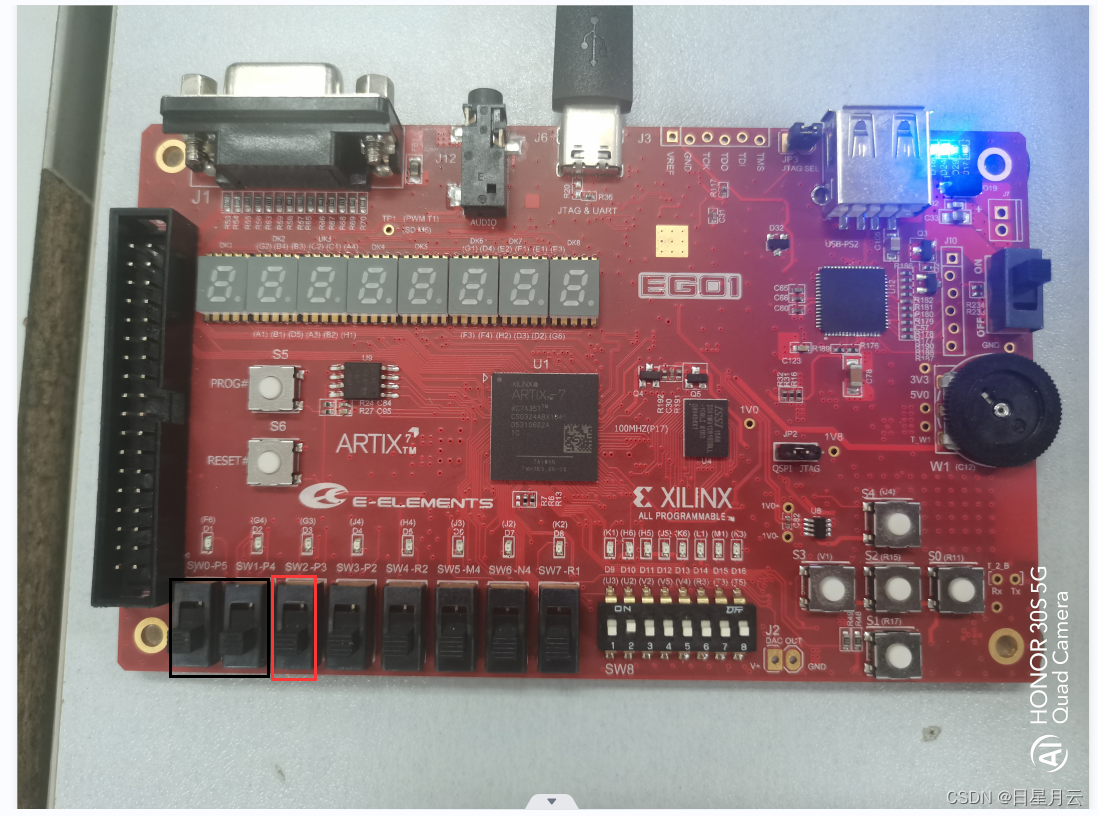

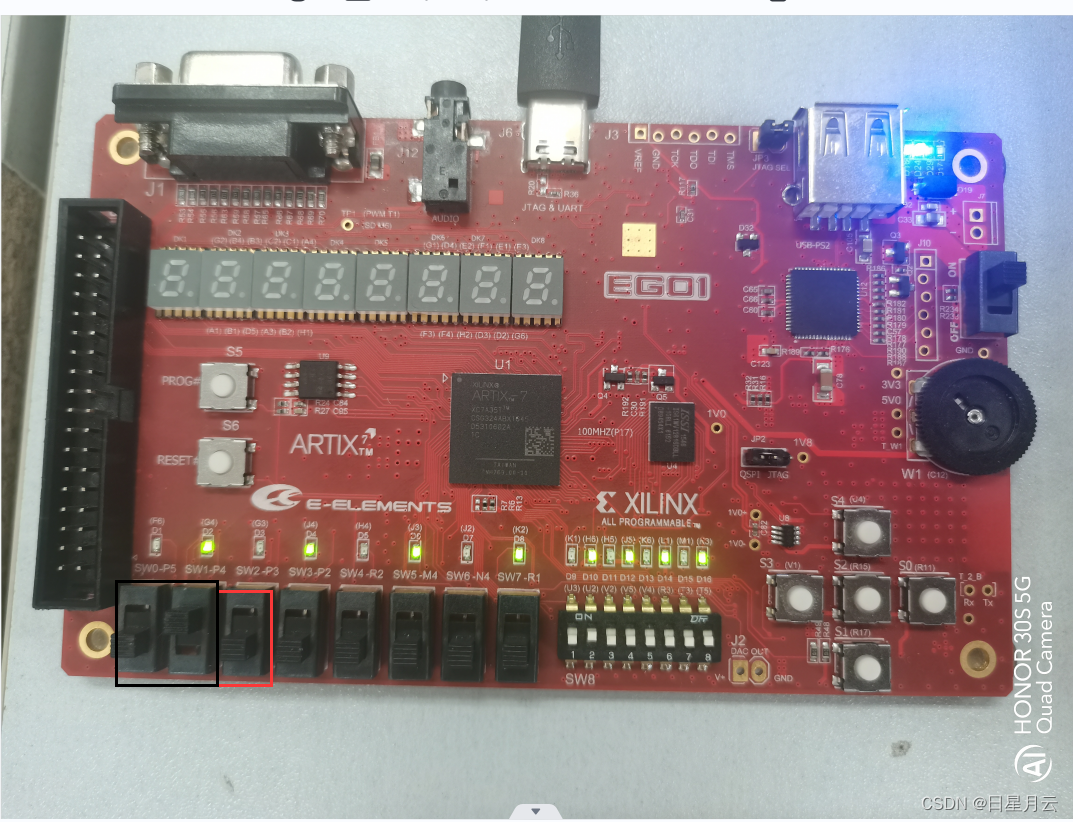

之后就可以正常运行了

当开关0和1为2’b00时

灯从左往右是16’h0000

当开关0和1为2’b01时

灯从左往右是16’h5555

当开关0和1为2’b10时

灯从左往右是16’haaaa

当开关0和1为2’b11时

灯从左往右是16’h5555

其余设计

简单的流水灯

初始化

循环只需把r3进行移位操作,sw给Led的送数据即可

控制的流水灯

初始化

循环读入开关,判断控制信号

跳转到不同的分支地址

来对R3进行不同的操作,sw到Led中即可

定时器

可以使用定时中断

把led从低位到高位进行赋值

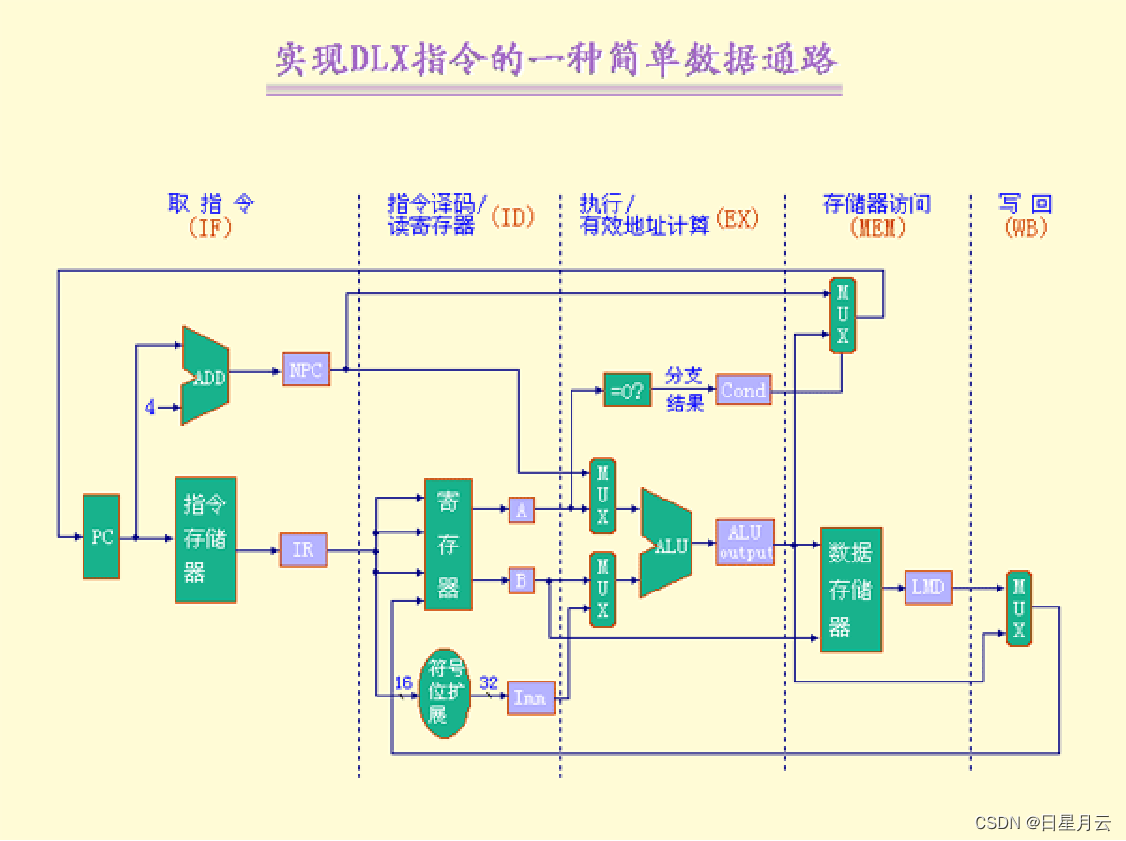

三、流水CPU的设计

MIPS的一种简单实现

有效地址计算提前到了ID中进行

给jCe jAddr传送到IF中

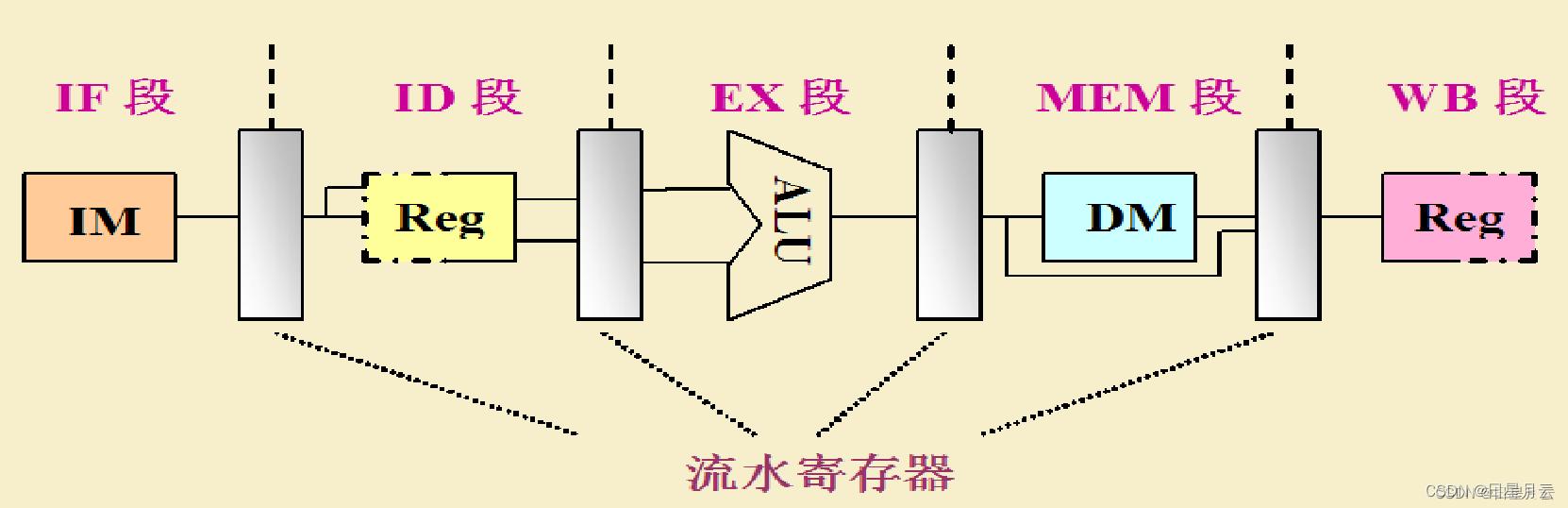

五段流水线CPU通路基本构成

1 测试指令流水

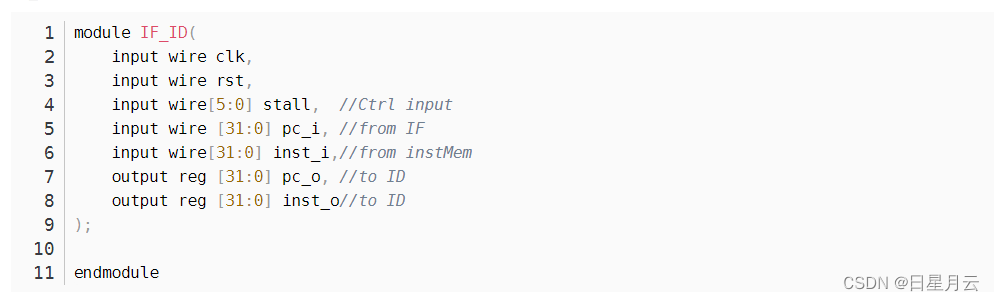

按我的理解是:

流水寄存器中输入输出的信号与前后两个模块相关

比如IF_ID:

输入信号:就是原IF给原ID传递的信号

输出信号:就是原ID接受原IF的信号

另外添加:clk与rst控制与存储inst取到的指令

所以流水寄存器

的引脚设计即为这样

功能设计类似与D触发器

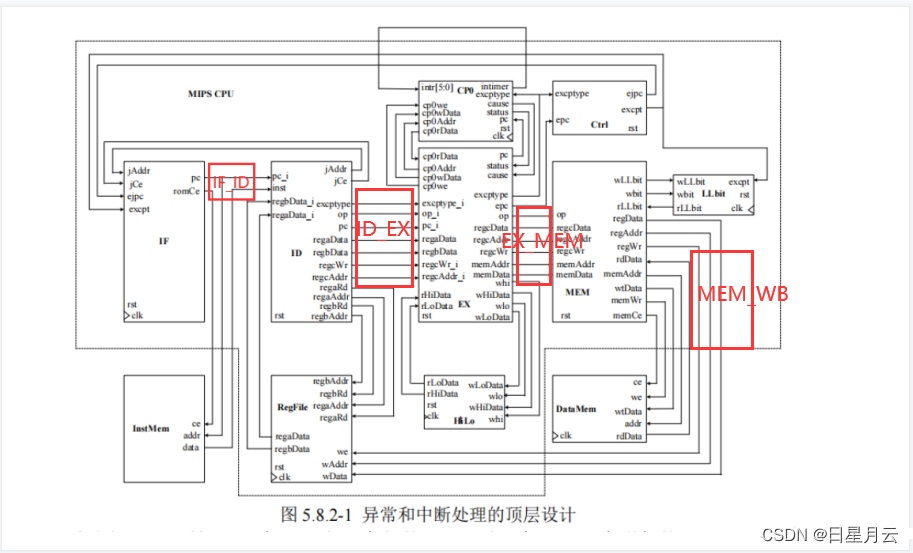

MIPS

需要把相邻两个模块拆开,用流水寄存器

相联

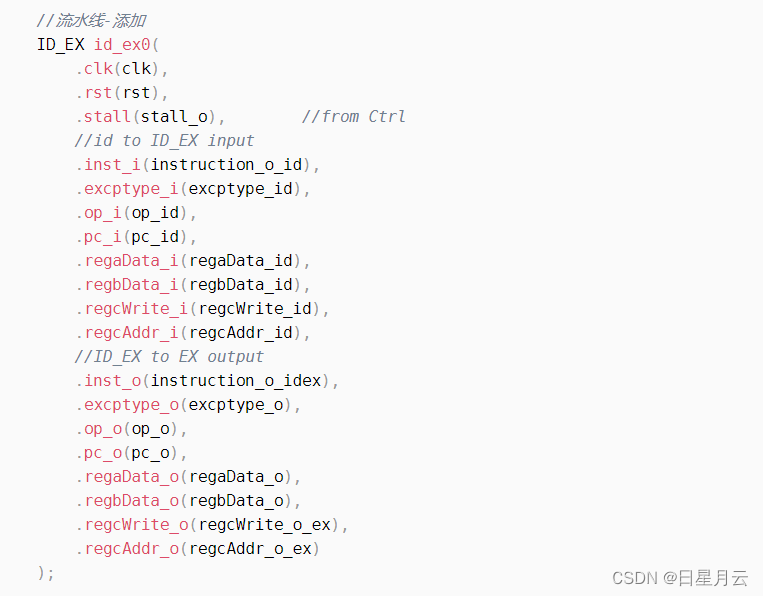

举例:说明怎么修改

比如:ID ID_EX EX

原来:ID输出–>EX输入

(一条线连接)

修改:

把原ID输出的信号–>ID_EX输入

把ID_EX的输出信号–>原EX输入

(两条线连接)

对比来看,把原EX输入信号量与ID_EX

输入相连

并且新增连线

把ID_EX的输出信号与原EX输入连接起来

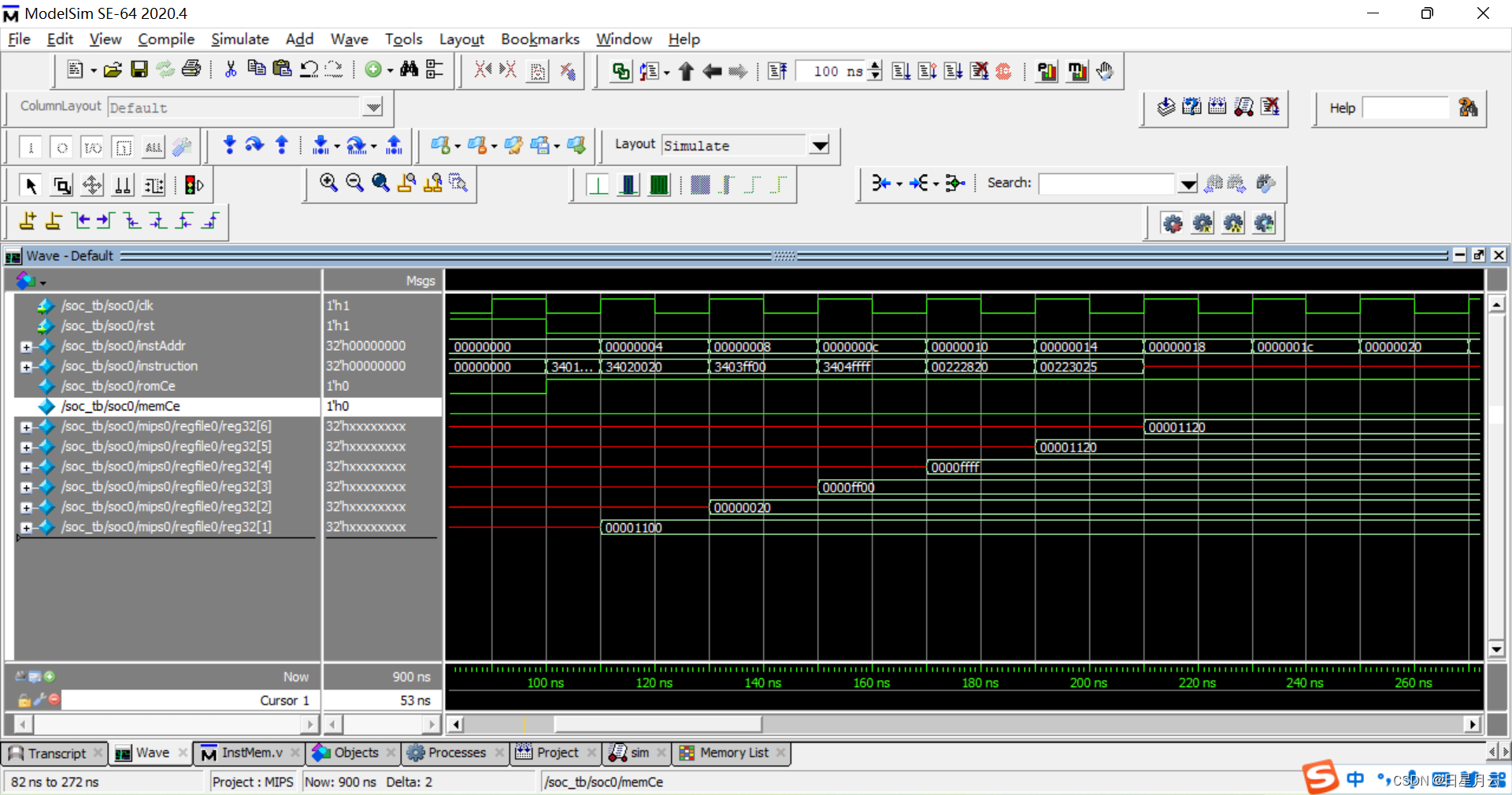

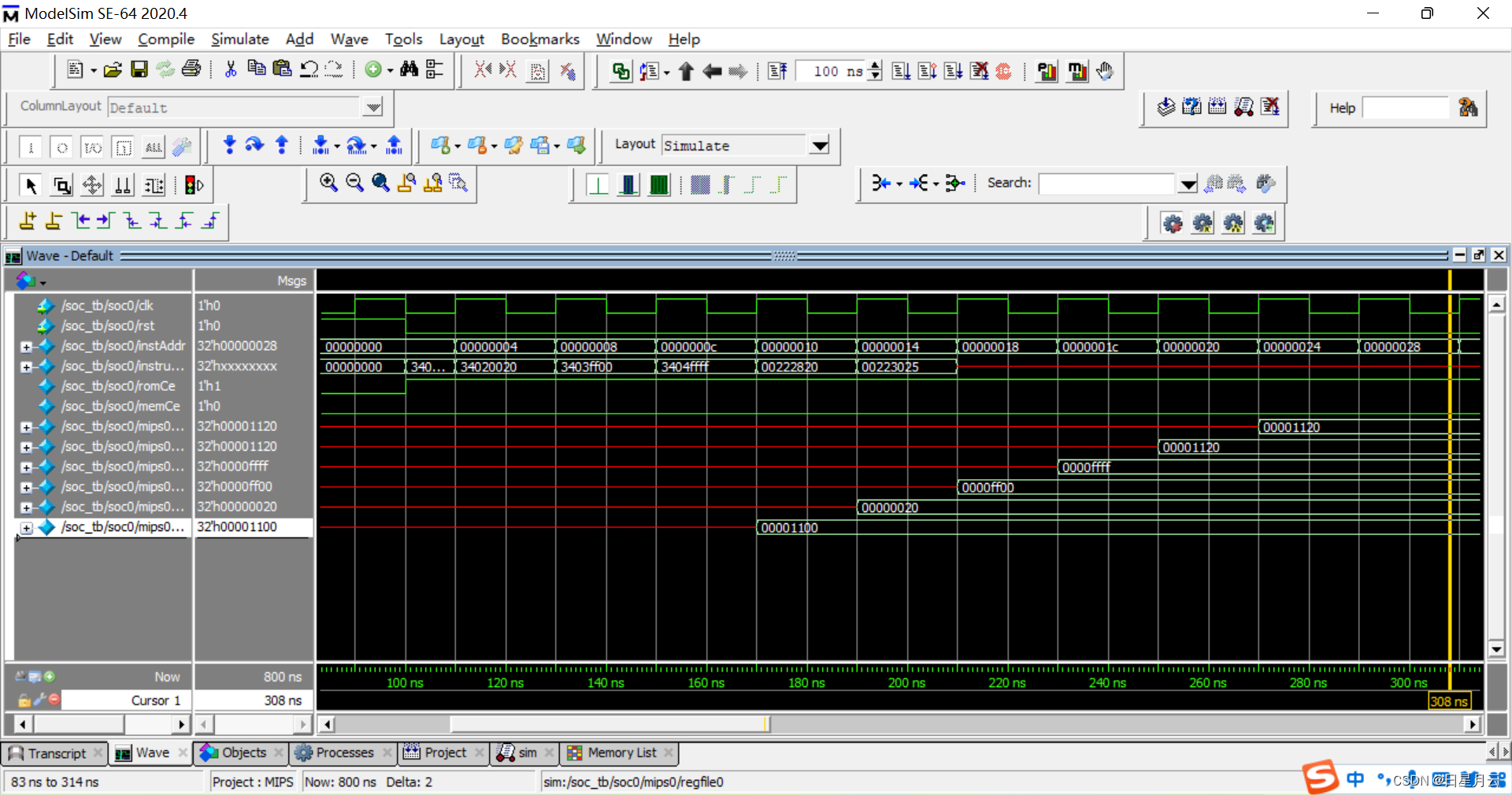

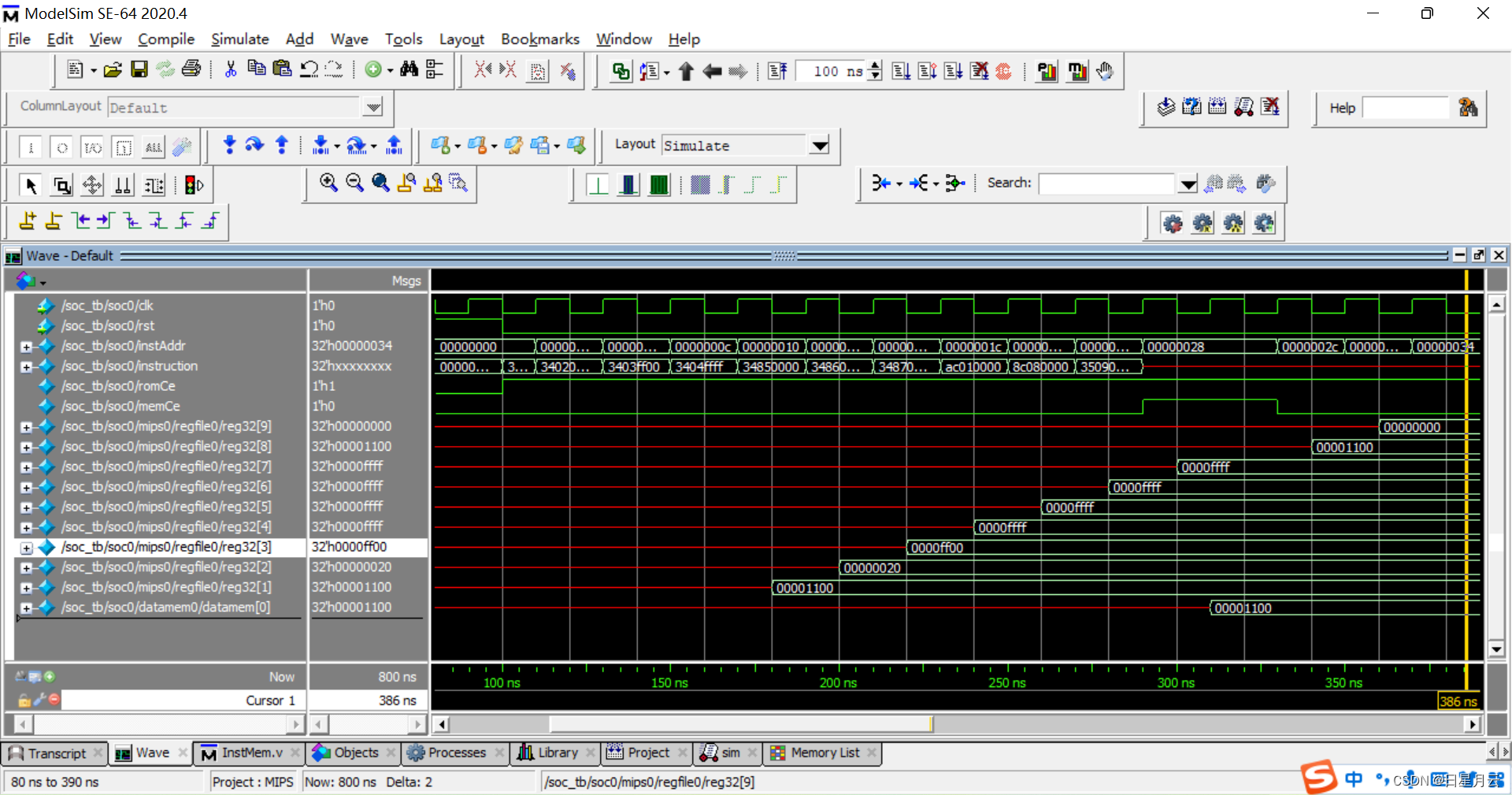

原来的单周期CPU的波形

一个周期产生一个数据

现在的流水CPU的设计波形

流水线满载(C)后,一个周期产生一个数据

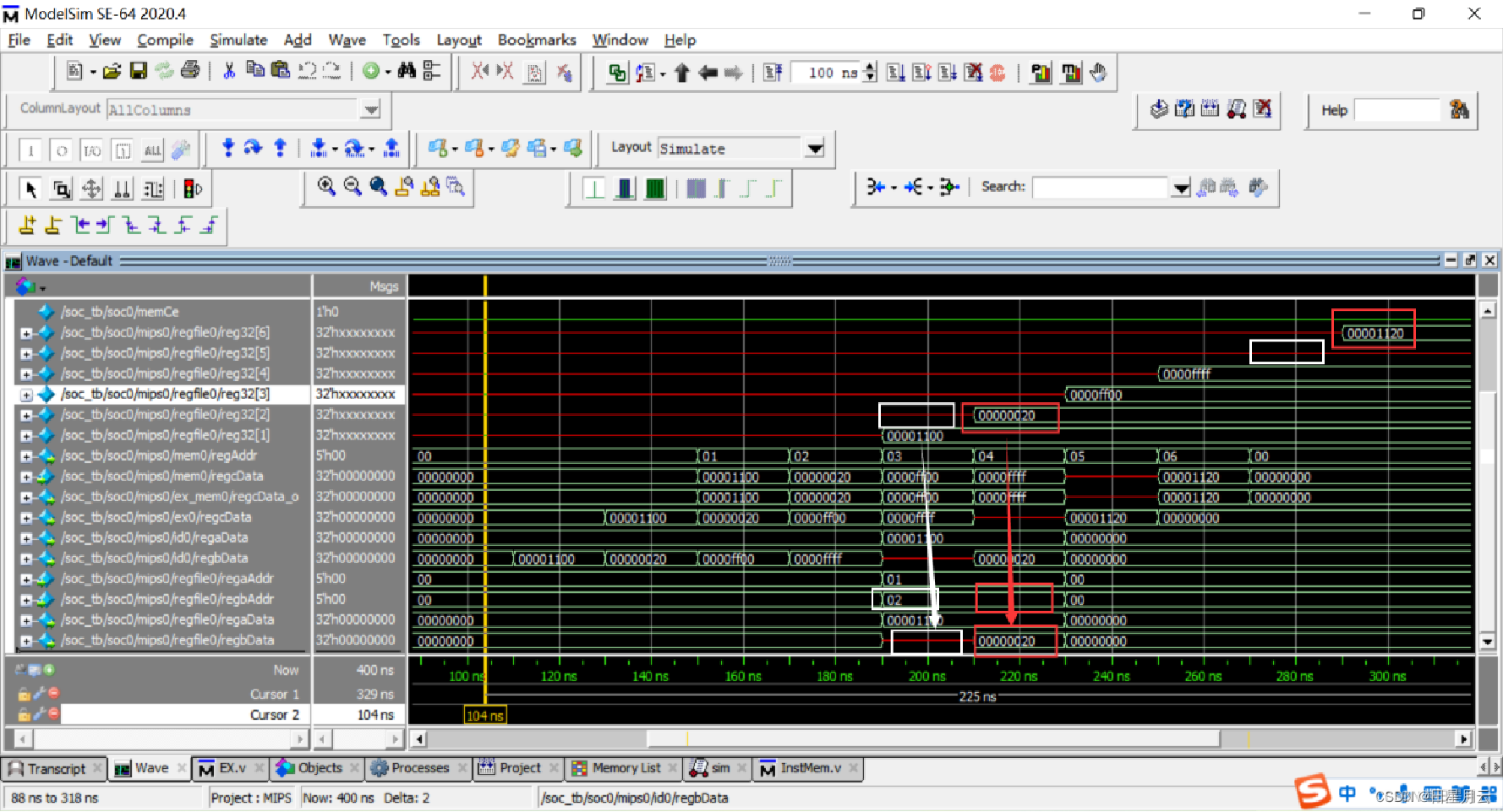

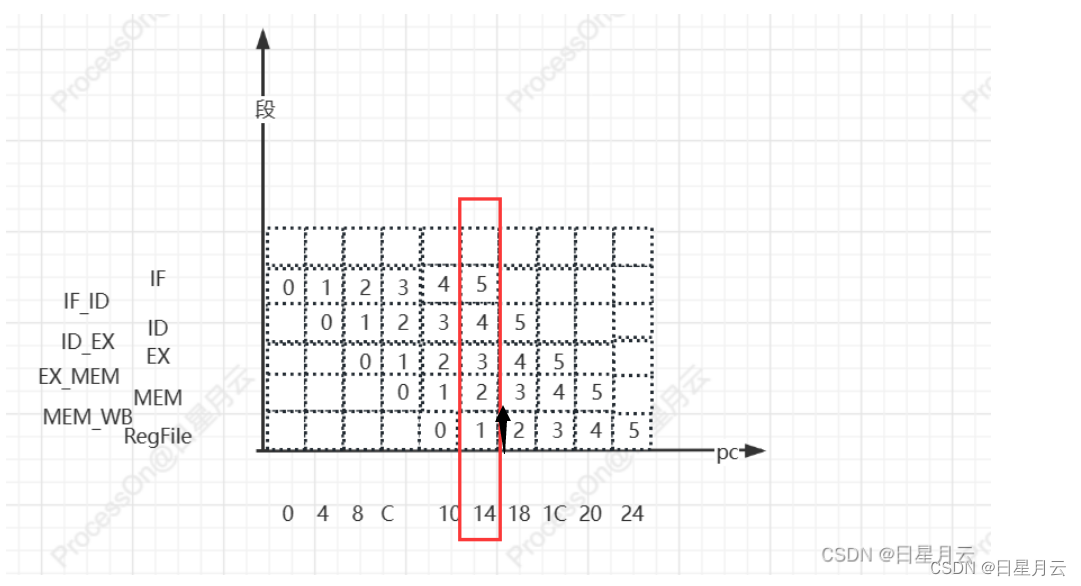

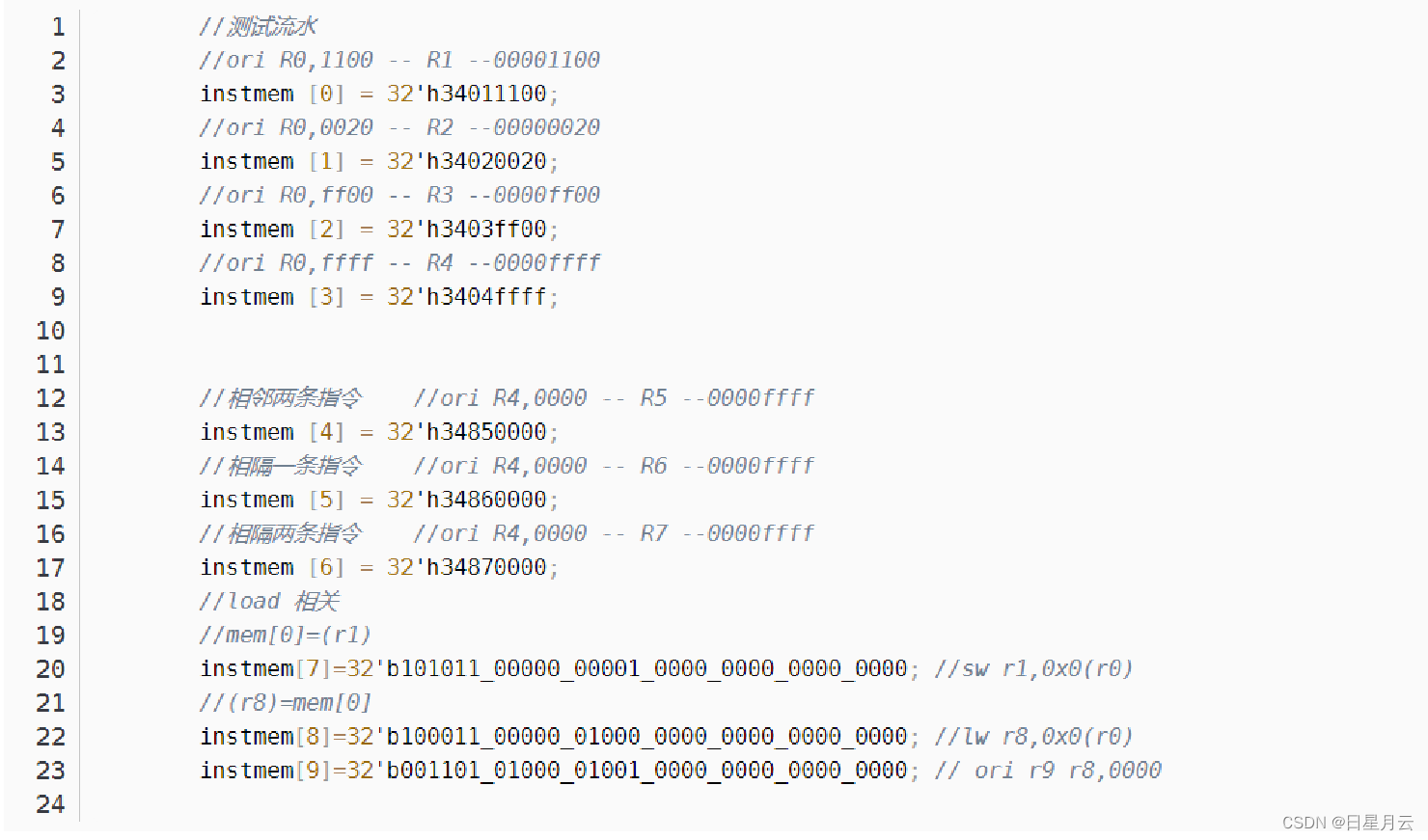

可以看到inst[1]和inst[4],中间隔离两条命令,所以有了数据冲突

当inst1执行到MEM时,准备写回R2时

inst4在ID段读出R2,还是没有值的,所以它的R5结果不对

但是inst5的R6结果是对的,因为这个时候R2的结果已经写入进去了

发现R5 没有结果,因为有数据冲突

pc=14时

可以看到inst4在ID段

但是inst1在WB段

在时钟上升沿

真正写入regFile

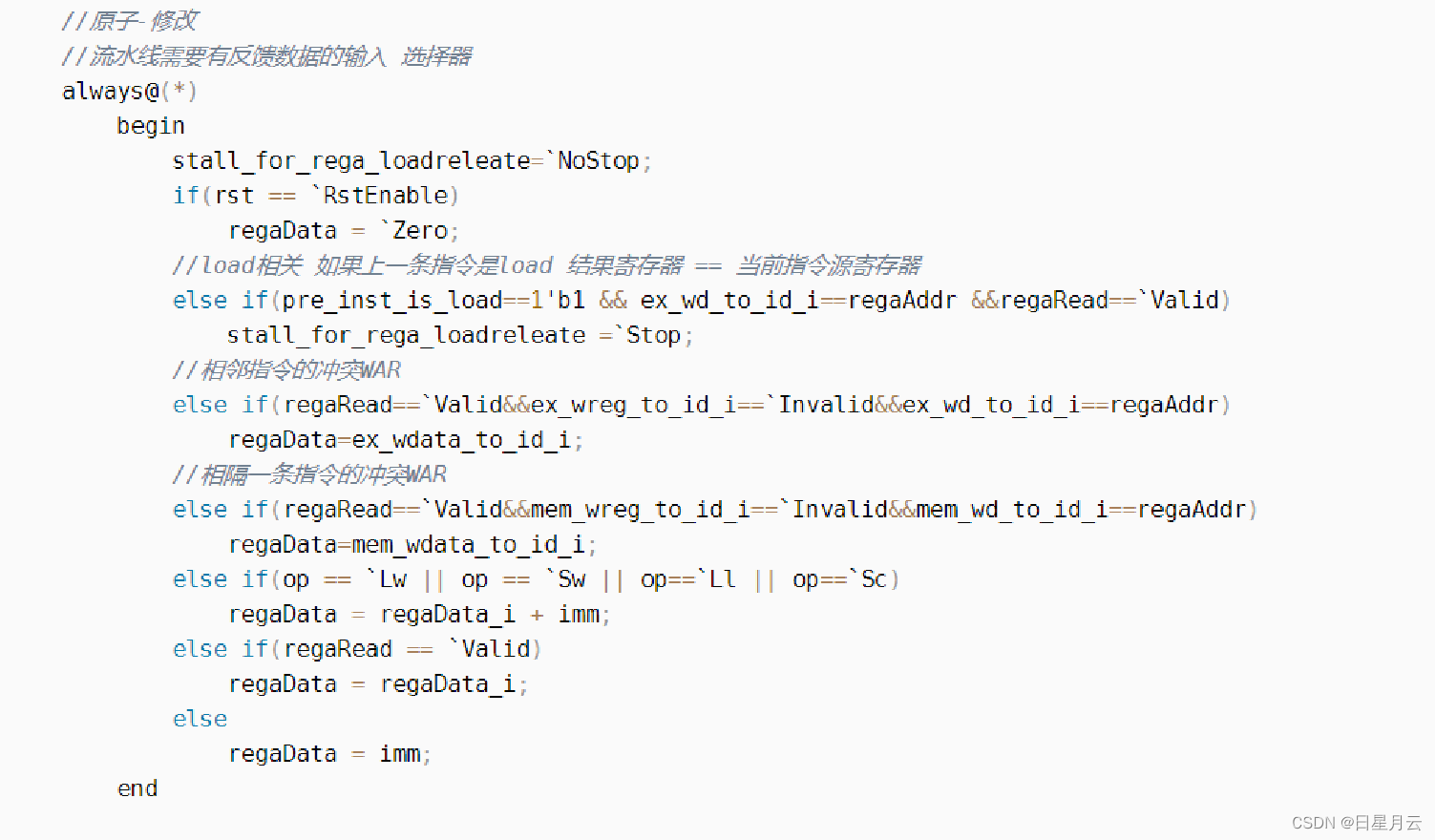

2解决数据冲突

数据冲突的分析

对于相邻WAR冲突

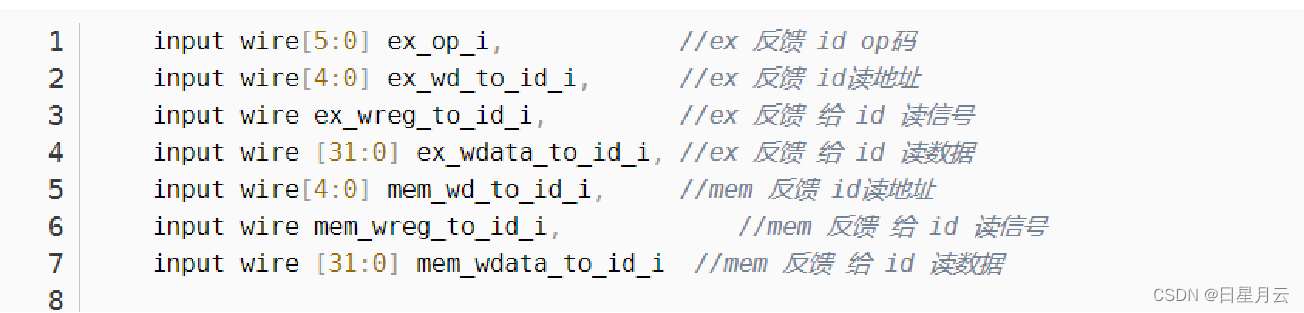

问题1:所以ID段的引脚设计需要怎么设计?

回答1:需要增加一个反馈接口从EX输出到ID输入

对于相隔一条WAR冲突

问题2:所以ID段和MEM的连线设计需要怎么设计?

回答2:需要增加一个反馈接口从MEM输出到ID输入

对于相隔两条WAR冲突

问题3:所以MEM段和regFIle的连线设计需要怎么设计?

回答3:需要增加一个反向器连接regFile的clk输入

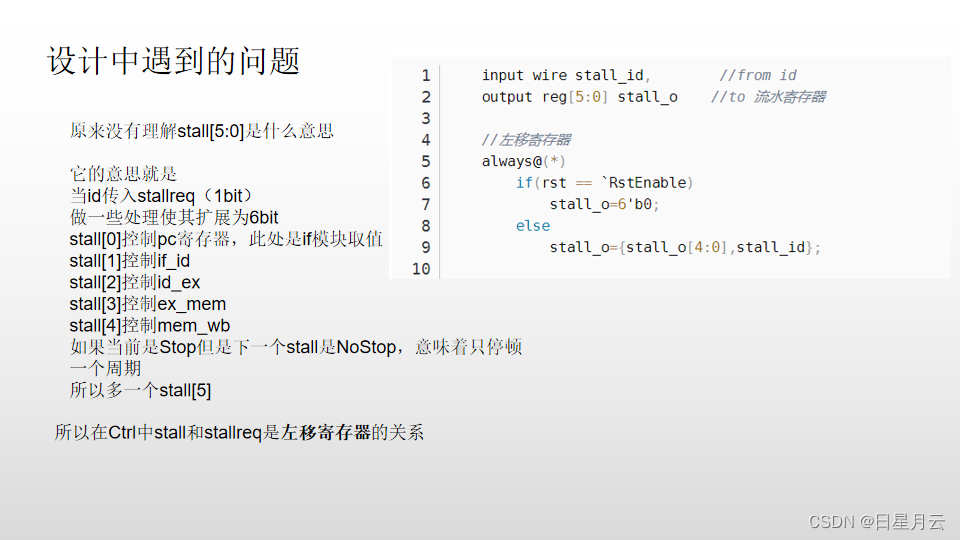

对于相邻Load相关

判断是否是Load冲突,停顿

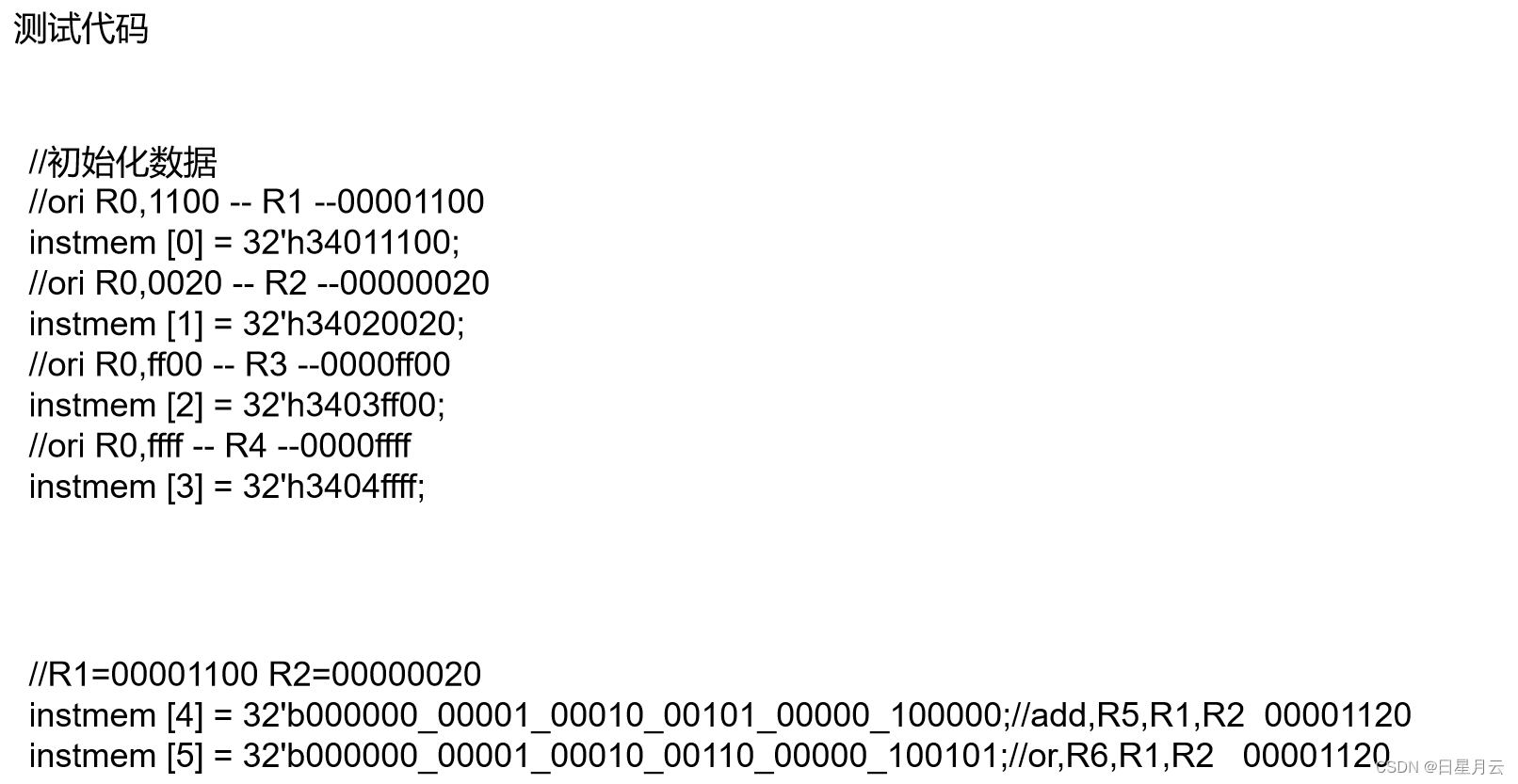

测试代码

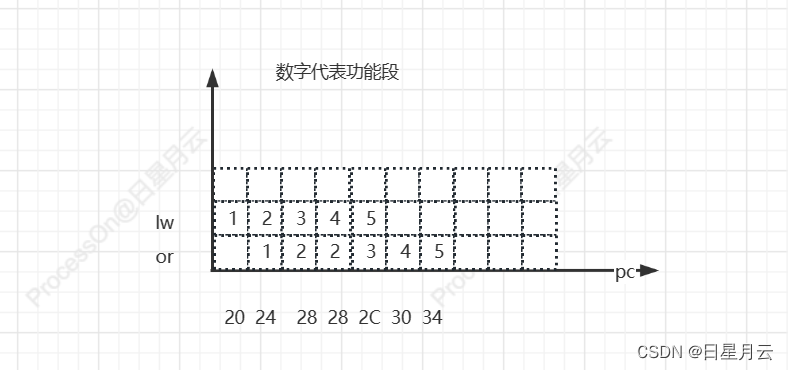

结果如下

load相关结果有点问题

load处理类似于

因为在pc=28时

or的ID段停顿了

但是regaData和regaRd清0了

导致结果有问题

ID的关于数据冲突的处理

附录

表1 20条MIPS整数指令

表2 MIPS 12条整数指令

表3 MIPS 与中断异常相关6条指令

最后

2023-6-1 22:10:34

所有资料均参考于老师的教学资料

所有代码均为自己手敲

所有内容均已发布到CSDN@日星月云

你对我百般注视,

并不能构成万分之一的我,

却是一览无余的你。

祝大家逢考必过

点赞收藏关注哦