第3章 嵌入式动态随机存储器

6T SRAM存储单元由六个晶体管组成,单元面积相对较大。为了增加存储密度,eDRAM是SRAM最具有潜力的替代品,根据存储单元不同分类:

- 传统的单晶体管单电容的(1T1C)eDRAM,其存储单元由一种特殊的高密度3D电容器和单个存取晶体管构成

- 增益单元eDRAM(GC-eDRAM),其存储单元通常由2到4个晶体管构建

3.1 1T1C eDRAM

3.1.1 单元结构

1T1C结构如图3-1所示,其单元由一个NMOS与一个电容组成,晶体管作为单元的存取管(AT),其栅极与字线连接,源漏极分别与位线和电容相连,电容两个电极中用于存储电荷的电极称为SN,电荷代表所存的数据。

图片来源于《嵌入式存储器架构、电路与应用》

- 写操作:字线置为高电平,晶体管导通。位线上的信息可以通过存取管顺利写入到电容上,信息成功写入后将字线置低,存取管关断,写操作完成。

- 读操作:字线置为高电平,存取管导通。根据电容上电平高低决定是否对位线放电,信息成功读出后将字线置低,存取管关断,读操作完成。

3.1.2 基本模块及相应操作

图3-2为eDRAM中一个子块的基本架构,主要包括存储单元阵列、灵敏放大器、输入输出电路和行列译码器等。整个DRAM芯片通过时序控制电路、供电电路等模块控制每个子块的工作情况。eDRAM的核心是存储阵列中的存储单元,每个存储单元都有着对应的字线与位线,并按照地址关系通过字线与位线与其他存储单元连接。数据以电荷的形式存储在单元内的电容上,而与电容相连的晶体管起到开关管的作用,通过字线开关相应的晶体管,数据可以从单元中顺利读出或者写入单元,其余的电路都是用于辅助实现单元读写功能。

图片来源于《嵌入式存储器架构、电路与应用》

DRAM阵列的架构主要有两种类型,即开放式位线结构(OB)与折叠式位线结构(FB),如图3-3和图3-4所示。

图片来源于《嵌入式存储器架构、电路与应用》

3.1.3 1T1C存储单元设计中的挑战

eDRAM中1T1C存储单元面临的主要挑战来自于保持时间(RT)和面积的折中,而对1T1C存储单元改进本质上都是为了在先进工艺节点下,既能保持基于1T1C存储单元的eDRAM面积优势,又能维持保持时间。

1 电容

电容是构成eDRAM 1T1C存储单元的核心。在进行读操作时,通过字线导通晶体管,电容上存储的电荷会与位线进行分享,产生电压差后再通过与位线连接的灵敏放大器放大位线上的电压差,最终将存储的数据读出。

eDRAM 1T1C存储单元的电容从平面型电容逐渐发展出两个不同的方向:深槽型电容(DTC)和堆叠型电容(SC)

2 开关晶体管

一个标准的eDRAM单元存在6个漏电路径,如图3-12所示分别是:结漏电、栅诱导漏极漏电、截止电流、单元间漏电、电容电介质漏电和通过浅沟道隔离漏电。与开关晶体管有关的漏电是前三个。

图片来源于《嵌入式存储器架构、电路与应用》

为了减小开关晶体管的漏电电流,两种方式:

- 增加开关晶体管的栅极电压摆幅。在需要读写的时候增加栅极电压,保证读写时功能正确;在需要关断时,减小栅极电压,甚至为负压,保证开关晶体管完全关断,减小截止电流。该方式缺点是开关晶体管的栅氧厚度需要增加

- 仔细考虑源极和漏极中结的掺杂分布来限制由结电场增加而导致的漏电。这种方式的缺点是尽管漏电被减少了,但是随着工艺尺寸的不断进步,器件的宽度和可驱动的电流都在显著降低,限制读写功能

3 刷新

在DRAM芯片中,数据以电荷的形式存储在单元的电容上,随着时间的推移,电荷会不断泄露。因此,为了防止数据丢失,DRAM需要周期性地重写每个单元,将单元电容中的电荷恢复到原来的水平。

DRAM的刷新策略分为两种:

- 突发式刷新,在一段时间内进行连续的刷新操作,直到所有单元都被刷新,再进行正常的内存访问

- 分布式刷新,在一个刷新周期内轮流刷新所有单元,在此期间DRAM可以保持一直进行正常的内存访问

3.1.4 IBM在处理器中有关eDRAM的设计

在IBM整个eDRAM设计中,除了架构上和单元上的优化,非常有名的还有POWER系列中采用的三级灵敏放大器设计,如图3-15与图3-16所示。通过这一设计,可以利用缩短位线有效提升存储器的速度及单元与位线的电容比。

图片来源于《嵌入式存储器架构、电路与应用》

图片来源于《嵌入式存储器架构、电路与应用》

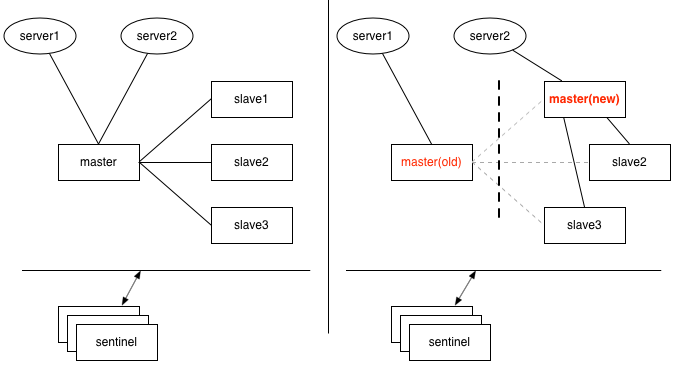

3.2 Gain Cell eDRAM

在提高单元电容容值研究方面,一种新颖的思路是利用增益单元结构(GC)规避提高电容的设计难点。GC eDRAM是一种6T SRAM和1T1C eDRAM折中选择的产物,它结合了SRAM(与数字CMOS技术兼容)和1T1C eDRAM(高存储密度)的优点,同时规避了SRAM(单元面积大)和1T1C eDRAM(破坏性读取、回写操作和需要特殊工艺步骤)的缺点。

但是,与SRAM相比,GC eDRAM的主要缺点仍然是其数据保持的动态特性,需要定期进行刷新操作。

3.2.1 2T GC eDRAM

最小的2T GC eDRAM电路如图3-18所示,由一个写晶体管(QW)与一个读晶体管(QR)组成,其中读晶体管也是存储晶体管。

图片来源于《嵌入式存储器架构、电路与应用》

- 读操作:读字线(RWL)置为高电平,读晶体管根据存储节点的电平决定是否对读位线(RBL)充电

- 写操作:写字线(WWL)置为低电平,写晶体管开启,写位线(WBL)上的信息通过写晶体管写入存储节点。

3.2.2 3T GC eDRAM

3T GC eDRAM由三个PMOS组成,如图3-19所示为基于65nm工艺下的电路图。工作原理与2T GC eDRAM类似:

- 写操作:写字线(WWL)置为低电平,写晶体管(PW)开启,写位线(WBL)上的信息通过PW写入存储节点

- 读操作:读字线(RWL)置为低电平,读晶体管(PR)导通,存晶体管(PS)根据存储节点的电平决定是否对读位线(RBL)充电

如图3-20所示为改进型的3T GC eDRAM:

图片来源于《嵌入式存储器架构、电路与应用》

3.2.3 4T GC eDRAM

基于28nm体硅工艺下,一种4T GC eDRAM结构被提出,电路结构如图3-21所示。

图片来源于《嵌入式存储器架构、电路与应用》

- 写操作:WWL置为高电平,晶体管NW和NB导通,WBL上数据传入存储节点SN

- 读操作:RBL被预充电到高电平,而RWL则被下拉到低电平,根据存储数据的不同决定是否对RWL放电

3.2.4 基于OSFETs的GC eDRAM

日本的半导体能源实验室从器件角度出发,提出用氧化物半导体场效晶体管(OSFET)结合传统CMOS工艺设计了2T1C的GC eDRAM,电路结构如图3-22所示。

图片来源于《嵌入式存储器架构、电路与应用》

3.3 HMC

除了改良单元结构来优化eDRAM的性能以外,提出新的eDRAM架构也是一种当前热门的研究方向,其中最具代表性的是Micron提出的混合存储立方体(HMC)架构,如图3-23所示。

图片来源于《嵌入式存储器架构、电路与应用》

具体架构和工作原理以Micron公布的HMC1.1为例进行说明,其内部架构如图3-24所示。

图片来源于《嵌入式存储器架构、电路与应用》

HMC使用低阶交错策略来映射内存块如图3-25所示。块大小是16B,所以低阶四位被忽略,接下来的地址位定义访问HMC时的最大块大小。

图片来源于《嵌入式存储器架构、电路与应用》

Ahn等提出扩展处理器的ISA使其支持存内计算来实现简单的PIM操作,从而不改变现有的编程模型。同时,通过改进硬件结构,根据数据是否在本地,自适应地通过考虑数据局部性来确定执行指令的位置,即存内计算或传统计算,具体架构图如图3-26所示:

图片来源于《嵌入式存储器架构、电路与应用》

致谢《嵌入式存储器架构、电路与应用》

希望本文对大家有帮助,上文若有不妥之处,欢迎指正

分享决定高度,学习拉开差距