目录

- 1. hdmi_colorbar_top设计

- 2. dvi_transmitter_top设计

- 3. OBUFDS 转换差分信号

- 4. 复位程序分析

- 5. 最终实验结果

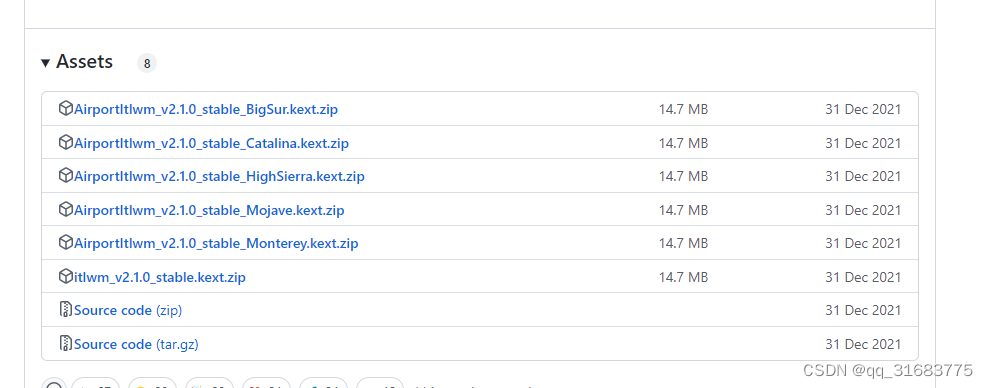

时钟生成 IP 核(clk_wiz_0)生成 1280*720 分辨率所需的像素时钟 74.25MHz、以及TMDS 编码驱动 IP 核所需的像素时钟的 5 倍频率即 74.25 * 5 = 371.25MHz。RGB 驱动模块(rgb_driver)负责产生 RGB 时序,并输出来自 RGB 显示模块(rgb_display) 的 RGB 数据。RGB 数据被送入 TMDS 编码驱动 IP 核(rgb2dvi_0)并最后输出到 HDMI接口。

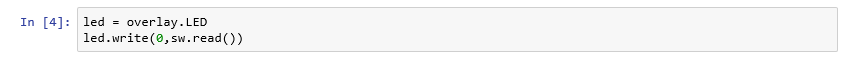

1. hdmi_colorbar_top设计

| hdmi_colorbar_top | 输入 | 位宽 | 定义 | 输出 | 位宽 | 定义 |

|---|---|---|---|---|---|---|

| sys_clk | 1 | 系 |