基本思想

容错量子计算的基本想法是,在合理编码后的量子态上直接量子计算,以至于不完全需要解码操作。假设有一个简单的量子电路,但不幸的是噪声影响着这个电路的每一个元件,包括量子态的制备、量子逻辑门、对输出的测量,甚至量子信息在电路中的简单传递。

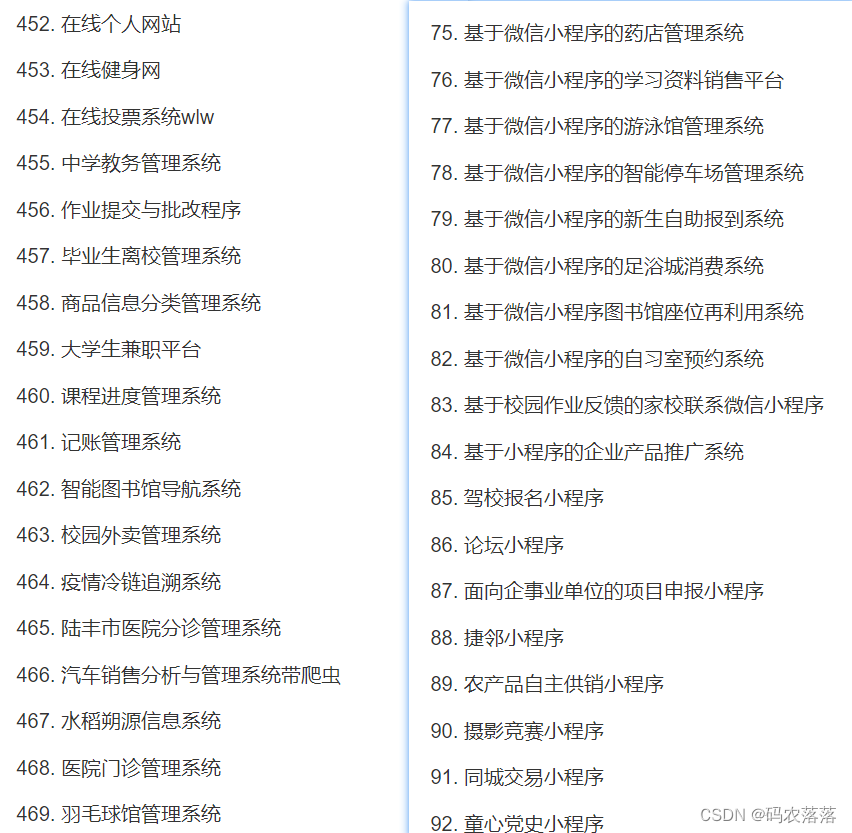

一个简单量子线路

为了对抗噪声的影响,利用7量子比特steane码的纠错码编码方式,将原电路中的每一个量子比特用一个量子比特区块来表示代替。同时将原电路中的每一个逻辑门用作用在逻辑量子比特上的编码逻辑门来代替。

用编码量子比特和编码逻辑操作的一个模拟实现,如果所有操作都是容错实现的那么输出的错误概率为,p为单个器件的失败概率。

通过周期性地在编码后的量子态上进行纠错操作,能够阻止错误在量子态中的积累,当然仅仅周期性的纠错是不足以阻止噪声的出现。原因是有两方面的,首先最重要的是编码逻辑门可能会导致错误的传播。如图编码的逻辑非门的错误会传到目标位置的量子比特上,即前者的错误会传到后者,为了让纠错能有效的消除噪声,在编码逻辑门执行过程中任何位置的错误,只能传到编码位置区块的少数位置。即这样的电路被称为容错电路。这样就可以用容错程序实现一系列量子逻辑门——阿达玛门、相位门、受控非门和门。量子纠缠第二个需要处理的问题是,纠错程序也会引入错误,因此必须小心设计纠错程序。

一个实例

我们现在来仔细考察一个实现容错受控非门,以及容错纠错步骤的程序,如图所示。对这个电路的分析分为四步。第一步是进入电路的输入时刻,第二步是编码受控非门作用后的时刻,第三步是征状测量之后的时刻,第四步是恢复操作完成之后的时刻。我们的目标是指出这个电路在第一个编码区块引人两个或多个错误的概率大概是,这里p是电路中单组成部分发生错误的概率。因为一个作用在第一个量子比特区块上的(假想的)完美解码程序,只有在该区块发生两个或多个错误时才会失败。因此,在上述电路完成之后,一个完美解码的量子态然包含错误的概率,跟电路作用之前相比至多大

。

为了证明这个程序在第一个量子比特区块中引入两个错误的概率是 ,我们来确定引入两个错误的所有可能性:

1.在第一步,在每个编码量子比特区块中都有一个已存在错误进入电路。这种情况有可能在输出的第一个量子比特区块中造成两个错误,因为,比如说第二区块中的错误可能会通过编码受控非门传播到第一个区块中来。假设到这步为止的所有操作都是容错的,我们可以认为,这种错误进入第一个区块的概率最多是,这里c是一个常数,原因是在量子电路之前的阶段,肯定有类似的错误发生在征状测量或信息恢复步骤。c是在电路前一阶段的征状测量或信息恢复步骤里可能发生错误的位置的总数。如果为了简单起见,我们假设在第一步某个已存在单量子比特错误进入第二区块的概率也是

。而且,这两个错误独立发生,那么它们同时发生的概率是

。对下面描述的Steane编码构造来说,有6个不同的征状测量对co有贡献,每一个都大概有101个位置可能发生错误。再结合信息恢复操作涉及7个组成部分的事实,我们可以估计出

≈70。

2.一个已存在错误进人第一个或第二个量子比特区块,同时在容错受控非门执行期间发生一个错误。这种情况发生的概率是,这里c1是类似错误可能发生的所有不同位置对的数量。就基于 Steane 编码的构造来说,之前我们提到过,两个区块中的每个有大概 70个可能的位置发生问题,导致一个错误进入电路,这样总共是140个位置。同时,有其他7个可能的位置在电路执行期间发生错误。因此,总共有a≈7x140≈103个可能的位置组发生一对错误。

3.在容错受控非门执行期间发生两个错误,这种情况发生的概率是,这里

是可能发生错误对的数量,对Steane编码,

。

4.在受控非门执行阶段和征状测量中各发生一个错误。在输出中发生两个或多个错误的唯一可能是征状测量给出错误结果,其发生的概率是,这里

是一个常数(对 Steane 编码来说

)。另外一种有意思,但其实无关紧要的情况是征状测量给出正确结果,此时受控非门引人的错误被正确诊断及纠正,因此输出中只剩下征状测量中引人的错误

5.征状测量中发生两个甚至多个错误,这种情况发生的概率是,这里c4是错误可能发生5.的位置对的数量。对Steane 编码来说,c4≈702≈5x

6.征状测量和信息恢复阶段各发生一个错误,这种情况发生的概率是,这里c5是错误可能发生的位置对的数量。对Steane编码来说,

。

7.信息恢复阶段发生两个甚至多个错误,这种情况发生的概率是cp?,这里c6是错误可能发生的位置对的数量。对 Steane编码来说,。

级联编码和阈值定理

基于级联编码的想法,我们可以通过实现一个漂亮的构造来进一步降低等效的错误率。其大致的思路是将上述以编码的方式实现逻辑电路的方案重复执行,以分层的形式构造出一系列量子电路,Co(原本我们希望实现的电路),C,C…。在构造的第一阶段,原电路中的每个量子比特被编码成量子编码,而编码中的每个量子比特又被进一步编码,如图10-22所示可以无休止地重复这个过程。在构造的第二阶段,原电路C中的每个逻辑门,例如阿达玛门,在电路中被容错实现的编码阿达玛门及对应的纠错电路替代。然后,C中的每个基本组成部分在C中又被容错实现的部件和对应的纠错电路替代,如此反复。假设我们如此实现两层级联编码,而底层-即实际的物理量子比特层--组成部分的错误率是p,那么中间层(一层编码)的错误率将是c?,而最高层(二层编码)的错误率是c(cp?)。注意为了保证计算的结果正确,最高层的功能实现必须完全正确。因此,如果编码的级联层数是k,则最高层的错误率是(cp)2/c,而整个电路的尺寸将是d乘以原电路的尺寸,这里d是一个常数,代表着容错实现编码逻辑门和对应纠错所需基本操作的最大数目。

如果我们希望如此实现一个包含p(n)个逻辑门的量子电路,这里,是问题的规模,p(n)是一个关于n的多项式。例如,这个电路可能是量子质因数分解算法的对应电路。假设我们希望最后以的精度实现这个算法,那么算法中每个逻辑门的精度需要至少是

。因此,级联编码的层数满足:

(1)

才能实现目标。选取k的最小值,于是式子接近等号,再重写可得:

(2)

poly为固定阶数的多项式,那么最终的电路包含

(3)

个逻辑门,只比原电路的尺寸大多项式倍。

那么阈值定理:一个逻辑门数量为p(n)的量子电路可以被一个包含

(4)

个逻辑门的电路以至多为的整体失败概率模拟实现,只要后者中单个组成部分的最大错误概率p低于某个常数阈值,即

,同时相关硬件中的噪声满足一些合理要求。

与阿达玛门、泡利门、泡利门不同,容错CNOT门需要steane编码,且泡利X和Z门,会导致错误的反向传播。