此内容仅是为了自己方便回忆,内容来源于野火指南者开发板教程。

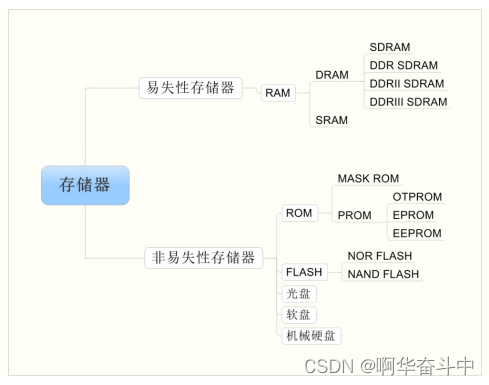

一.存储器

RAM(Random Access Memory)随机存储器:当存储器中的消息被读取或写入时,所需要的时间与这段信息所在的位置无关。

RAM分为动态随机存储器DRAM(Dynamic RAM)和静态随机存储器SRAM(Static RAM)

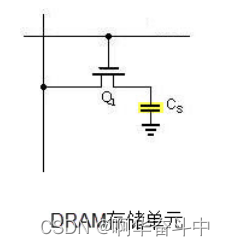

DRAM:以电容的电荷来表示数据,有电荷表示1,无电荷表示0;时间一长,有电的电容会放电,没电的电容会吸电,因此要定期刷新操作,动态由此而来。

由DRAM通讯方式分为:同步和异步;由于时钟同步的通讯速度更快同步DRAM使用更广泛,称为SDRAM(Synchronous DRAM)

DDR SDRAM存储器(Double Data Rate SDRAM):SRAM在上升沿表示有效数据,一个时钟周期内只能表示1个有效数据,DDR SDRAM在上升沿和下降沿各表示一个数据,1个时间周期内表示2位数据。DDRII和DDRIII主要是提高了通讯同步时钟的频率

SRAM:以锁存器来存储数据,不需要定时刷新充电

根据SRAM通讯方式分为同步(SSRAM)和异步(SRAM)。

DRAM和SRAM比较:

ROM(Read Only Memory)只能读的存储器:分为不可修改的MASK ROM、一次可编程存储器OTPROM(One Time Programable ROM)、可重复擦写的存储器EPROM(Erasable Programmable ROM)、电可擦除存储器EEPROM(Electrically Erasable Programmable ROM)

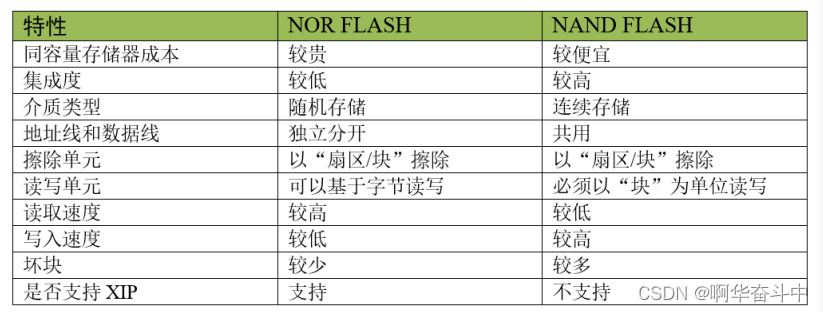

FLASH存储器(闪存):

NOR FLASH一般应用在代码存储的场合,如嵌入式控制器内部的程序存储空间

NAND FLASH 一般应用在大数据量存储的场合,包括SD卡、U盘、固态硬盘

二.IIC读写EEPROM

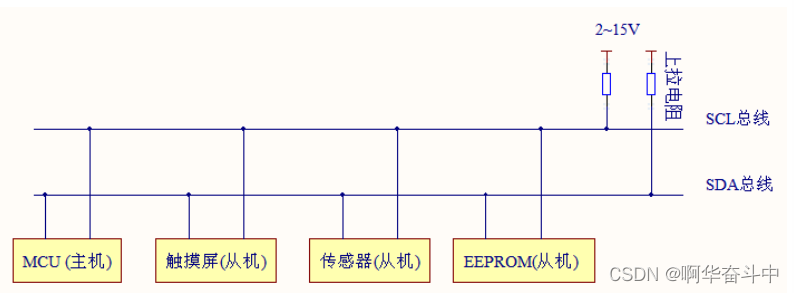

IIC通讯系统:

物理层特点:支持设备的总线(“总线”:多个设备公用的信号线);使用2条总线线路SDA(双向串行数据线)和SCL(串行时钟线);每个设备都有一个独立的地址;总线通过上拉电阻连接电源,IIC空闲时输出高阻态,所有设备空闲时,所有输出高阻态,上拉电阻把总线拉成高电平;有仲裁方式;三种传输模式:标准模式100kbit/s,快速模式400kbit/s,高速模式3.4Mbit/s;连接相同总线的IC数量受总线的最大电容400pF限制。

协议层:

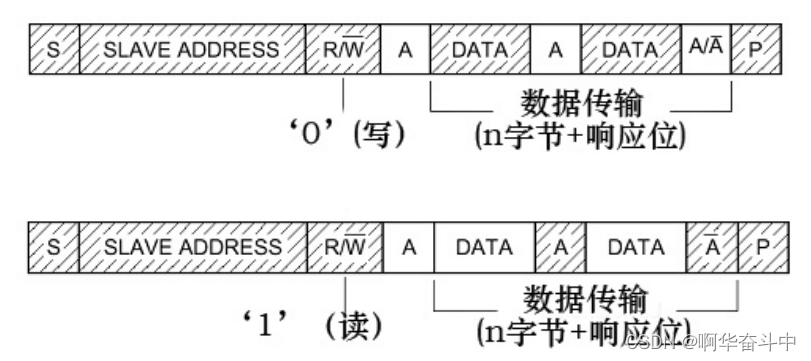

IIC读写过程:

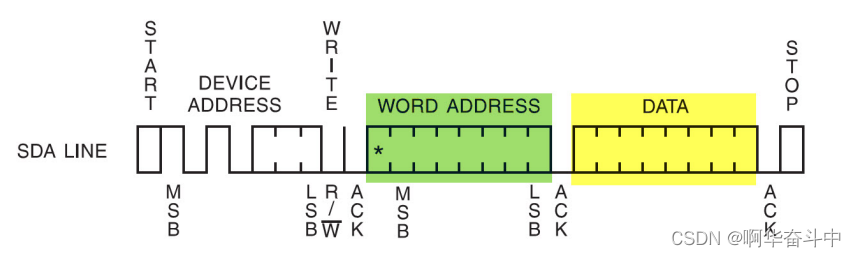

写数据(图一):接收到起始信号后,匹配从机地址(7位或10位),在配置方向位写入‘0’即写数据,然后传输数据(8位),主机每发完一个字节数据,都要等待从机的应答信号,如此循环写入数据,直到从机接收到停止传输信号P。

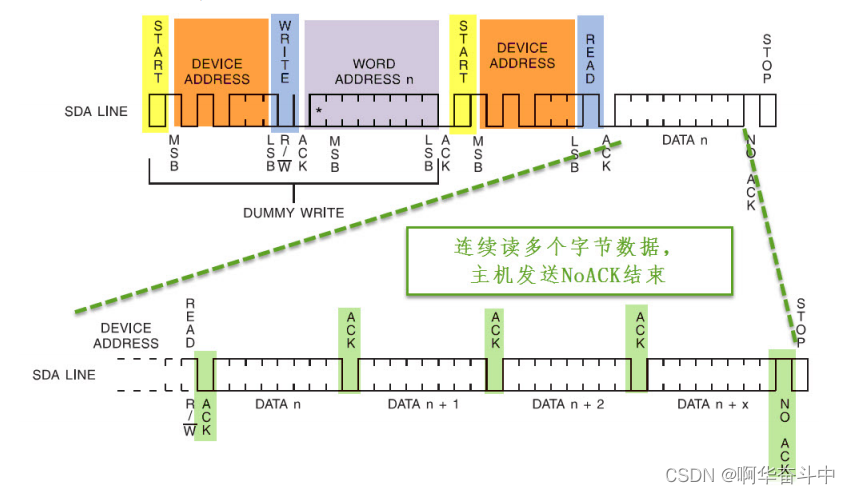

读数据(图二):接收到起始信号后,匹配从机地址(7位或10位),在配置方向位写入‘1’即读数据,然后接收数据(8位),从机每发送完一个字节数据,都要等待主机的应答信号,如此循环读入数据,直到主机返回一个非应答信号。

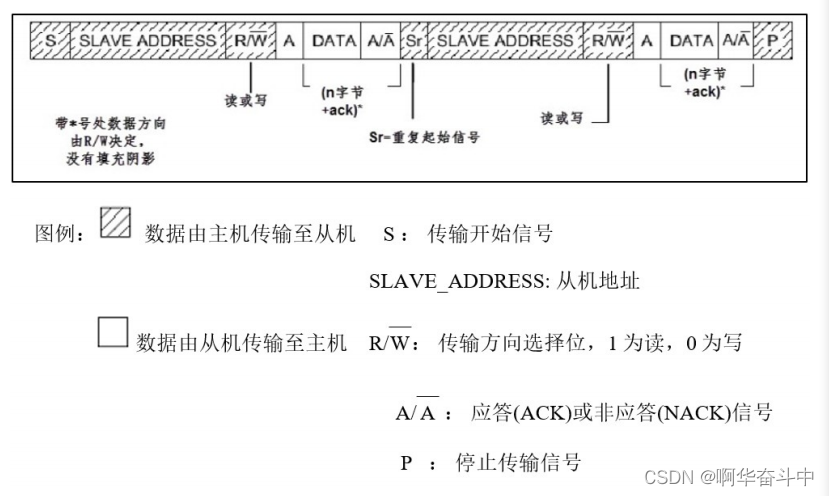

读和写数据:第一次通讯是告诉从机读写地址,第二次则是读写的实际内容。

通讯的起始和停止信号:

一般由主机产生,当SCL是高电平时,SDA线从高电平变成低电平表示通讯的起始;当SCL是高电平时,SDA线从低电平变成高电平表示通讯的停止。

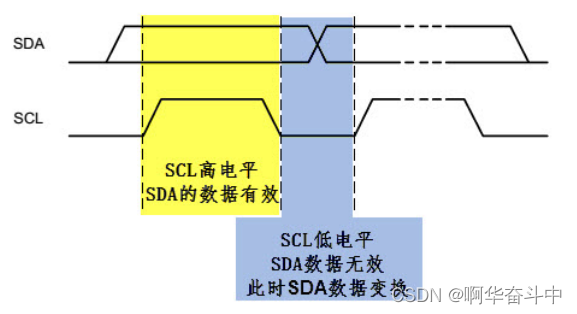

数据有效性:

当SCL为高电平时SDA表示的数据有效,此时SDA为高电平表示数据”1“,低电平表示数据”0“。当SCL为低电平时,SDA的数据无效。

地址及数据方向:

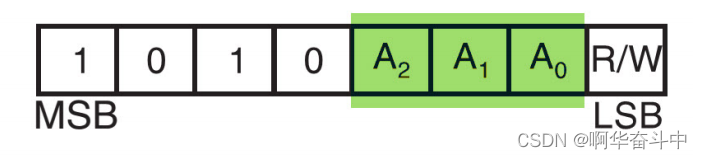

IIC协议规定设备地址是7位或10位,表示数据传输方向位在第8位或第11位,”1“表示读数据,”0“表示写数据。

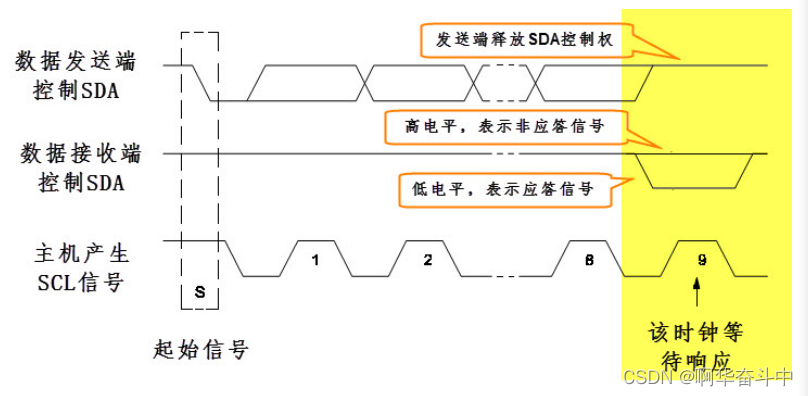

响应:包括”应答(ACK)“和”非应答(NACK)“

传输后,希望继续发送数据,要向对方发送”应答“信号;若希望结束数据传输,要向对方发送”非应答“信号。

IIC架构:

STM32F10x的IIC引脚:

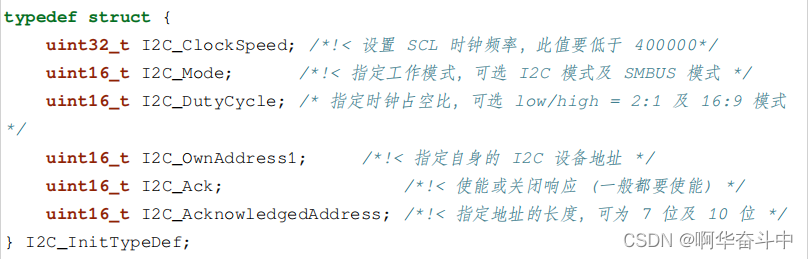

②:时钟控制寄存器(CRR)可选择”标准/快速“模式;在快速模式下可以选择SCL时钟占空比Tlow/Thigh=2或Tlow/Thigh=16/9模式;还有一个12位的配置因子,配置如下

标准模式:Thigh=CCR*Tpclk1*Tlow=CCR*Tpclk1

快速模式中Tlow/Thigh=2时:Thigh=CCR*Tpclk1*Tlow=2*CCR*Tpclk1

快速模式中Tlow/Thigh=16/9时:Thigh=9*CCR*Tpclk1*Tlow=16*CCR*Tpclk1

③:数据控制逻辑

④:整体控制逻辑

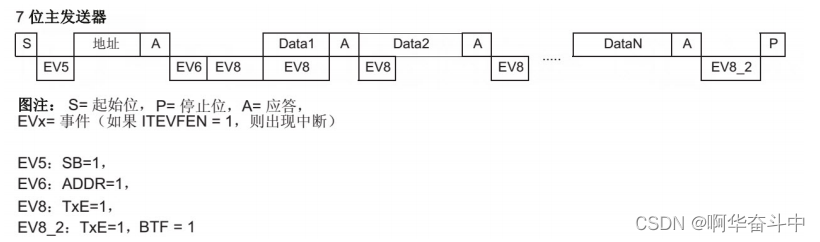

主发送器过程:

主接收器过程:

IIC结构体:

IIC——读写EEPROM实验:

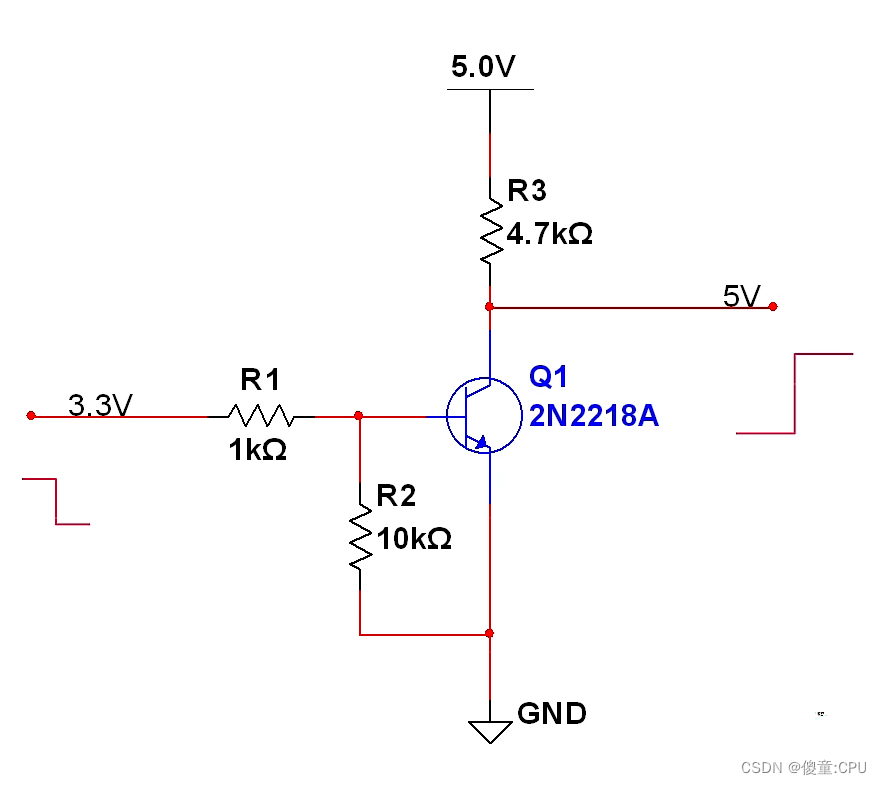

硬件设计:

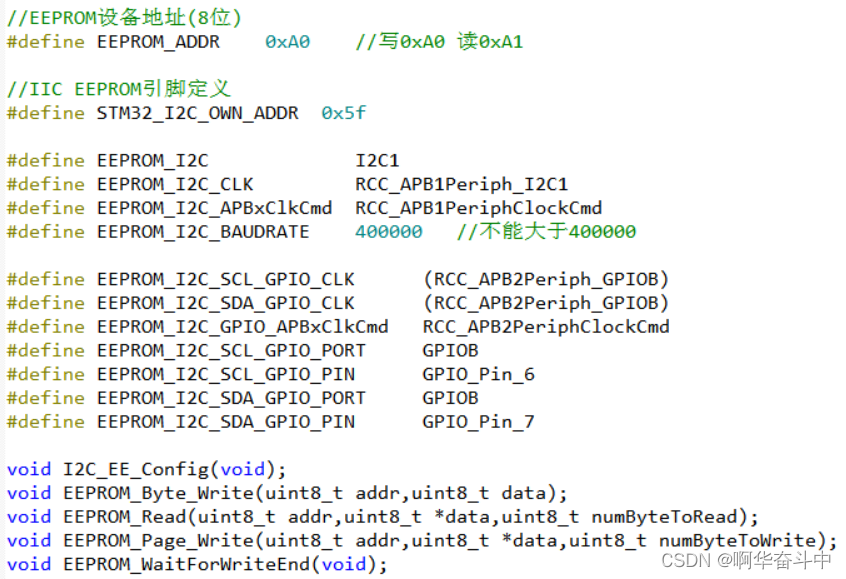

EEPROM设备地址一共7位,其中高4位固定为:1010b,低三位由A0,A1,A2决定,原理图A0,A1,A2接地,设备地址是1010000b(0x50)

写地址:0xA0;读地址:0xA1

WP引脚:具有写保护功能,高电平时禁止写入数据,低电平时可写入数据。

程序思路:

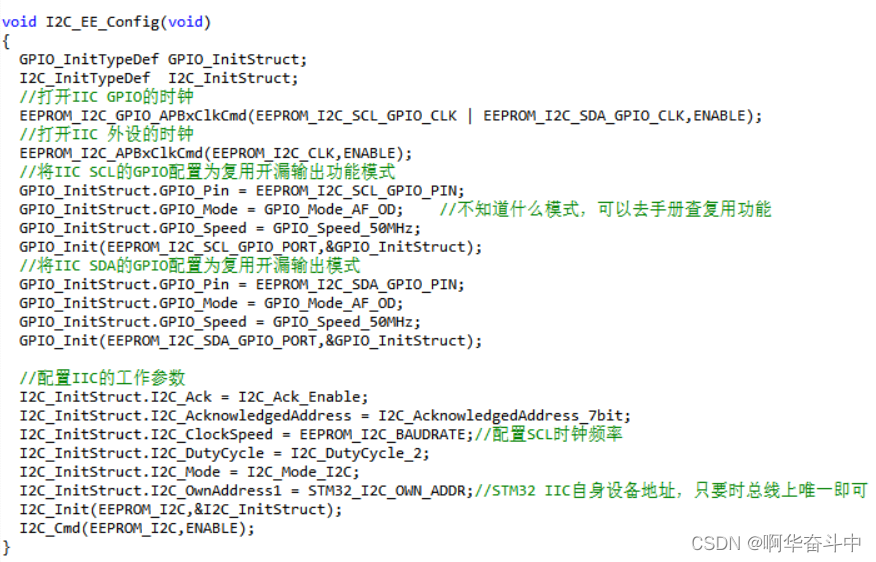

1.配置通讯使用的目标引脚为复用开漏模式

2.使能IIC外设时钟

3.配置IIC结构体

4.编写IIC按字节收发的函数

5.编写读写EEPROM存储内容的函数

6.通过串口对数据进行校验

iic.h配置:

iic.c配置:

iic初始化:

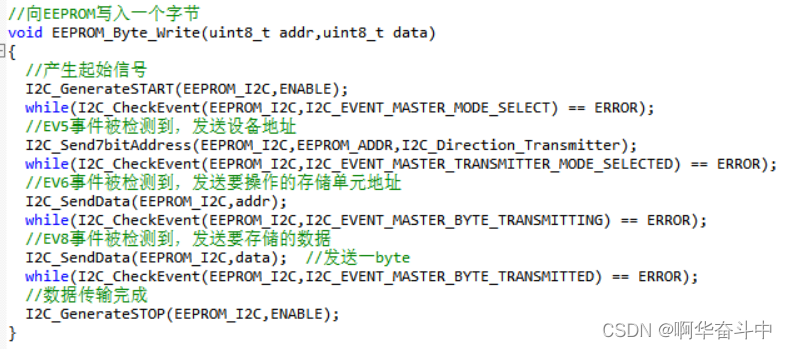

写入一个字节:根据时序图来写

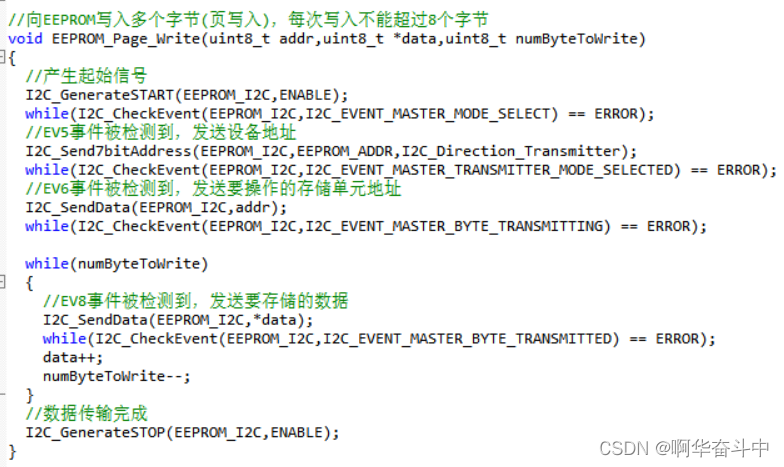

写入多个字节:根据时序图来写

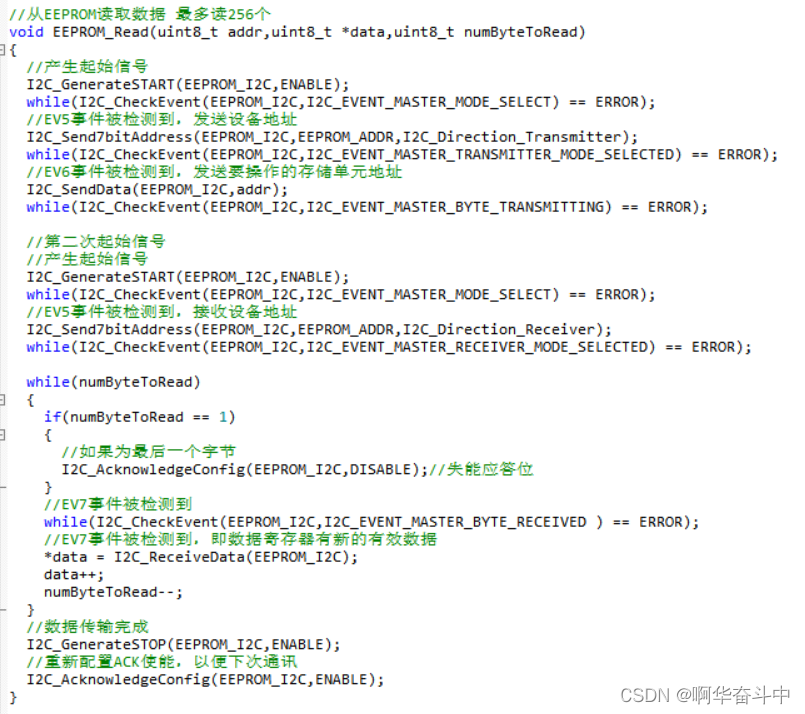

读取数据:根据时序图来写

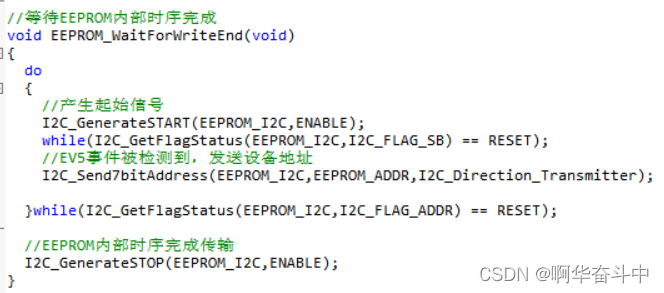

等待内部时序完成:每次写入或读出都要加,不然程序会跑不出结果

收获:遇到程序跑不出理想结果的时候,可以用在线调试,多给几个断点,全速运行到断点看有没有卡住,一点一点查问题,不要心烦气躁!!!

页写入好需要改进,由于EEPROM芯片的型号,只能写8个字节,并且要字节对齐,这个很关键,不然出来的结果和输入数据对不上,需要改进的代码可以去看野火STM32教学手册看!