通过阅读本文小节内容,可以清楚的明白汇编承接的能力和机器语言,高级语言之间的表达关系。文中虽然讨论16位cpu,最新的64或以后的128理论都一样的,类推就好了。

继续将 通用寄存器-汇编复习(1)_luozhonghua2000的博客-CSDN博客 完结,内容:汇编指令,物理地址,16 位结构的 CPU,8086CPU 给出物理地址的方法的本质含义

汇编指令

通过汇编指令控制 CPU 进行工作,看一下表 中的几条指令

注意,为了使具有高级语言基础的读者更好地理解指令的含义,有时会用文字描述和高级语言描述这两种方式来描述一条汇编指令的含义。在写一条汇编指令或一个寄存器的名称时不区分大小写。如: mov ax,18 和 MOV AX,18 的含义相同: bx 和 BX 的含义相同。

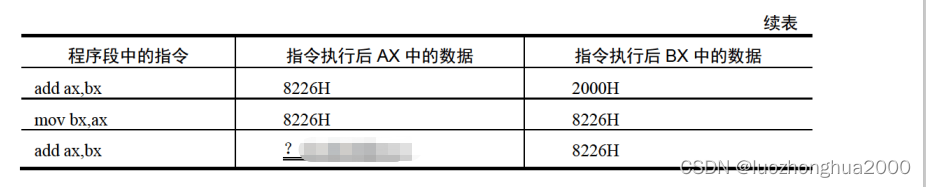

接下来看一下 CPU 执行表中所列的程序段中的每条指令后,对寄存器中的数据进行的改变。

指令执行后 AX 中的数据为多少? 思考后看分析。分析:

程序段中的最后一条指令 add ax,bx,在执行前 ax 和 bx 中的数据都为 8226H,相加(换算器?)后所得的值为: 1044CH,但是 ax 为 16 位寄存器,只能存放 4 位十六进制的数据(为啥?请参考通用寄存器-汇编复习(1)_luozhonghua2000的博客-CSDN博客 8086CPU 的所有寄存器都是 16 位的),所以最高位的 1 不能在 ax 中保存(为什么呢?为什么是最高位去掉?栈顶?),ax 中的数据为: 044CH。

指令执行后 AX 中的数据为多少? 思考后看分析

分析:

程序段中的最后一条指令 add al,93H,在执行前,al 中的数据为 C5H,相加后所得的值为:158H,但是 al 为 8 位寄存器,只能存放两位十六进制的数据,所以最高位的 1丢失,ax 中的数据为:0058H。(这里的丢失,指的是进位值不能在 8 位寄存器中保存,但是 CPU 并不真的丢弃这个进位值 ,后续回答)

注意,此时 al 是作为一个独立的 8 位寄存器来使用的,和 a 没有关系,CPU 在执行这条指令时认为 a 和 al 是两个不相关的寄存器。不要错误地认为,诸如 add al,93H 的指令产生的进位会存储在 a 中,add al,93H 进行的是 8 位运算。

如果执行 add ax,93H,低 8 位的进位会存储在 ah 中,CPU 在执行这条指令时认为只有一个 16 位寄存器 ax,进行的是 16 位运算。指 add ax,93H 执行后,ax 中的值为:0158H。此时,使用的寄存器是 16 位寄存器 ax,add ax,93H 相当于将 ax 中的 16 位数据00c5H 和另一个 16 位数据 0093H 相加,结果是 16 位的 0158H

在进行数据传送或运算时,要注意指令的两个操作对象的位数应当是一致的,例如:

等都是错误的指令,错误的原因都是指令的两个操作对象的位数不一致。

练习:

物 理 地 址

我们知道,CPU 访问内存单元时,要给出内存单元的地址。所有的内存单元构成的存储空间是一个一维的线性空间,每一个内存单元在这个空间中都有唯一的地址,我们将这个唯一的地址称为物理地址

CPU 通过地址总线送入存储器的,必须是一个内存单元的物理地址。在 CPU 向地址总线上发出物理地址之前,必须要在内部先形成这个物理地址。不同的 CPU 可以有不同的形成物理地址的方式。我们现在讨论 8086CPU 是如何在内部形成内存单元的物理地址的。

16 位结构的 CPU

我们说 8086CPU 的上一代 CPU(8080、8085)等是 8 位机,而 8086 是 16 位机,也可以说 8086 是 16 位结构的 CPU。那么什么是 16 位结构的 CPU 呢?

概括地讲,16 位结构(16 位机、字长为 16 位等常见说法,与 16 位结构的含义相同)描述了一个 CPU 具有下面几方面的结构特性。

8086 是 16 位结构的 CPU,这也就是说,在 8086 内部,能够一次性处理、传输、暂时存储的信息的最大长度是 16 位的。内存单元的地址在送上地址总线之前,必须在 CPU中处理、传输、暂时存放,对于 16 位 CPU,能一次性处理、传输、暂时存储 16 位的地址。

最新64位的cpu类推

8086CPU 给出物理地址的方法

8086CPU 有 20 位地址总线,可以传送 20 位地址,达到 1MB 寻址能力。8086CPU 又是 16 位结构,在内部一次性处理、传输、暂时存储的地址为 16 位。从 8086CPU 的内部结构来看,如果将地址从内部简单地发出,那么它只能送出 16 位的地址,表现出的寻址能力只有 64KB。

8086CPU 采用一种在内部用两个 16 位地址合成的方法来形成一个 20 位的物理地址8086CPU 相关部件的逻辑结构如图 1 所示。

如图 1 所示,当 8086CPU 要读写内存时:

1)CPU 中的相关部件提供两个 16 位的地址,一个称为段地址,另一个称为偏移地址;

2)段地址和偏移地址通过内部总线送入一个称为地址加法器的部件:

3)地址加法器将两个 16 位地址合成为一个 20 位的物理地址:

4)地址加法器通过内部总线将 20 位物理地址送入输入输出控制电路:

5)输入输出控制电路将 20 位物理地址送上地址总线;

6)20 位物理地址被地址总线传送到存储器。

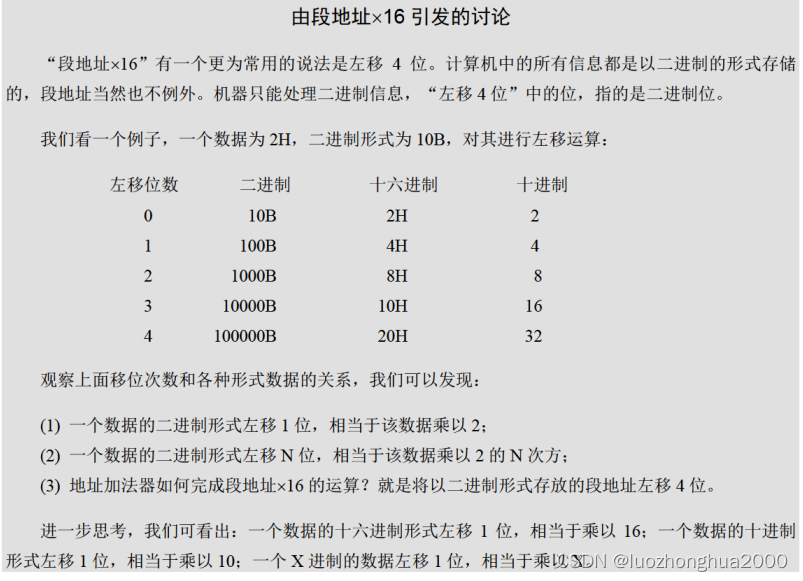

地址加法器采用物理地址=段地址x16+偏移地址的方法用段地址和偏移地址合成物理地址。例如,8086CPU 要访问地址为 123C8H 的内存单元,此时,地址加法器的工作过程如图 2所示(图中数据皆为十六进制表示)。

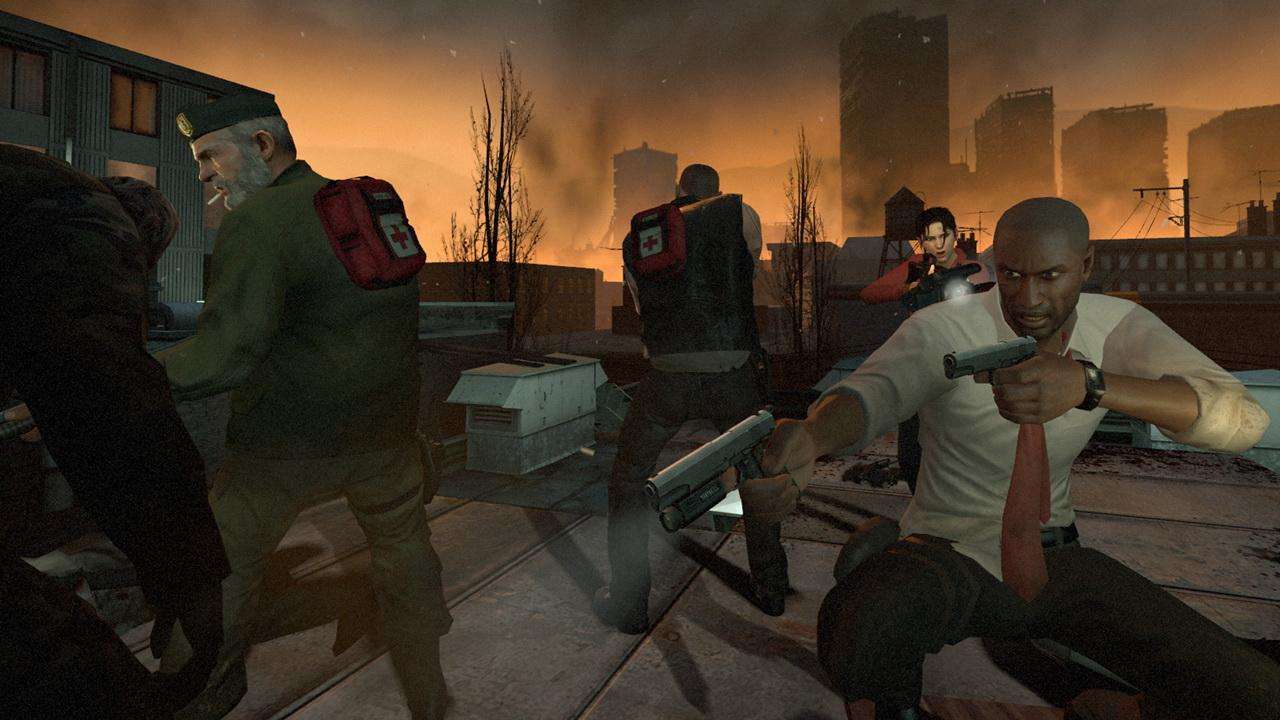

![[L4D]求生之路一代玩求生之路二代地图方法](https://img-blog.csdnimg.cn/3b131110d83f4b73bd7573fa30b09f4d.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L1pCemliaW5n,size_16,color_FFFFFF,t_70#pic_center)