目录

一、ARM架构

1.1.RAM---随机存储器

1.2.ROM---只读存储器

1.3.flash---闪存存储器

1.4.时钟(振晶)

1.5.复位

二、CPU---ARM920T

2.1.R0~R12---通用寄存器

2.2.PC程序计数器

2.3.LR连接寄存器

2.4.SP栈指针寄存器

2.5.CPSR当前程序状态寄存器

2.6.SPSR -CPSR备份寄存器

2.7.Cache缓存

2.8.MMU: 内存管理单元

2.9.ALU算数逻辑单元

三、处理器

四、总结

一、ARM架构

1.1.RAM---随机存储器

RAM---随机存储器特点--速度快,掉电数据丢失分类:SRAM---静态随机存储器DRAM---动态随机存储器SDRAM---同步动态随机存储器DDR(n)---内存条1.2.ROM---只读存储器

ROM---只读存储器特点--速度慢,掉电数据不丢失分类:PROM---可编程只读存储器EPROM---可擦除只读存储器EEPROM---电擦除只读存储器 1.3.flash---闪存存储器

特点---速度快,掉电数据不丢失 分类:norflash---基础单元就是 或非门 可线性访问nandflash---基础单元就是 与非门 不可线性访问线性访问---有专门的地址总线和数据总线(可以像内存一样访问)1.4.时钟(振晶)

时钟是同步工作系统的同步节拍,各个部分通过这个节拍来完成协调一致,从而实现协调配合。SoC内部有很多器件,例如CPU、串口、DRAM控制器、GPIO等内部外设,这些要实现协同工作,需要一个同步的时钟系统来指挥。这个就是我们的SoC时钟系统。

1.5.复位

ARM处理器的复位是一种初始化过程,它发生在系统启动或者发生故障后恢复运行时。当处理器处于复位状态时,它的内部寄存器、指令指针和内存状态都会被重置到预设的初始值,以便于开始执行固件(通常是最小的引导程序)中的第一条指令。这一过程有助于保证系统的可靠性和一致性,使得设备可以从停机状态或异常情况快速恢复正常操作。

二、CPU---ARM920T

2.1.R0~R12---通用寄存器

寄存器r0-r12是ARM处理器的通用寄存器,主要用来存储临时数据、函数参数和返回值。这些32位寄存器在不同场景有不同的用途,如r0-r3常用于参数传递,r4-r11存储临时数据,r12(IP)在某些版本中作为临时存储。此外,r13-r15是特殊寄存器,分别对应栈指针SP、链接寄存器LR和程序计数器PC。

2.2.PC程序计数器

程序计数器, 默认值为0, 做自加运算, 实际指向正在运行的下下条指令。

2.3.LR连接寄存器

保存函数的返回地址。

2.4.SP栈指针寄存器

指向栈定。

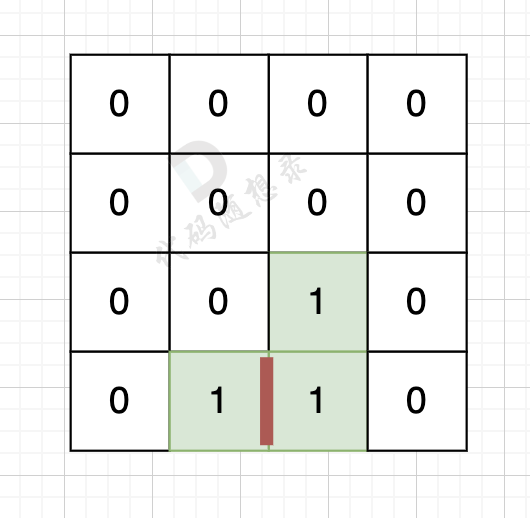

栈的种类有4种:---满增栈---满减栈---空增栈---空减栈ARM中我们使用的是满减栈。

为啥要使用满减栈 ?

从高地址开始进栈保存返回值,越界会进入堆区,产生越界错误,进程结束运行,而如果使用满增栈,越界会进入内核区,影响整个系统的运行;(减)

满增栈,每次将元素插入指针的位置,栈指针再后移一,出栈时,栈指针先减一,再元素出栈,最后一个元素出栈无法判断是否栈空了;而满减栈,每次先指针后移一次,再将元素插入指针的位置,使用栈的第一个位置会空出来,而出栈时,元素显出栈,指针再减一,可以再判断时,判断指针指向的空间是否为空,为空则说明栈空了;只有满减栈,才可以再出栈时判断栈是否空了。(满)

2.5.CPSR当前程序状态寄存器

运算结果为正、负、进借位、结果为0等标志, 中断的使能, 工作状态,工作模式;

2.6.SPSR -CPSR备份寄存器

2.7.Cache缓存

CPU缓存是位于CPU与内存之间的临时存储器,它的容量比内存小但交换速度却比内存要快得多。CPU高速缓存的出现主要是为了解决CPU运算速度与内存读写速度不匹配的矛盾。

因为CPU运算速度要比内存读写速度快很多,这样会使CPU花费很长时间等待数据到来或把数据写入内存。在缓存中的数据是内存中的一小部分,但这一小部分是短时间内CPU即将访问的,当CPU调用大量数据时,就可先从缓存中调用,从而加快读取速度。

两种Cache模型?

哈佛 数据和指令分开存储 ---读取效率高(可以同步读取数据和指令)

冯诺伊曼 数据和指令一起存储 ---读取效率慢

2.8.MMU: 内存管理单元

虚拟地址到物理地址的映射。

2.9.ALU算数逻辑单元

三、处理器

CPU:中央处理单元MCU:微控制器 51单片机MPU:微处理器 intelDSP:数字信号处理器FPGA:现场可编程门阵列 -- 硬件设计语言AHB:高速总线

APB:低速总线数据总线:是CPU与内存或其他器件之间的数据传送的通道地址总线:用于传输指示计算机中的内存或外设的物理地址控制总线:读写信号等RISC:精简指令集

CISC:复杂指令集处理器中的ARM920T也就是CPU,相当于微处理器,计算十分强大,但需要许多控制器来配合实现不同的功能。处理器也就有了许多控制器的加入。

四、硬件存储结构

五、总结

需要清楚知道APM架构的组成,以及其处理器的组成成分和CPU的组成成分。处理器中可以有很多个CPU也就是现在常说的几核处理器,CPU可有相同类型大小不同,也可以是不同的类型,可以把他们看作电路来理解。