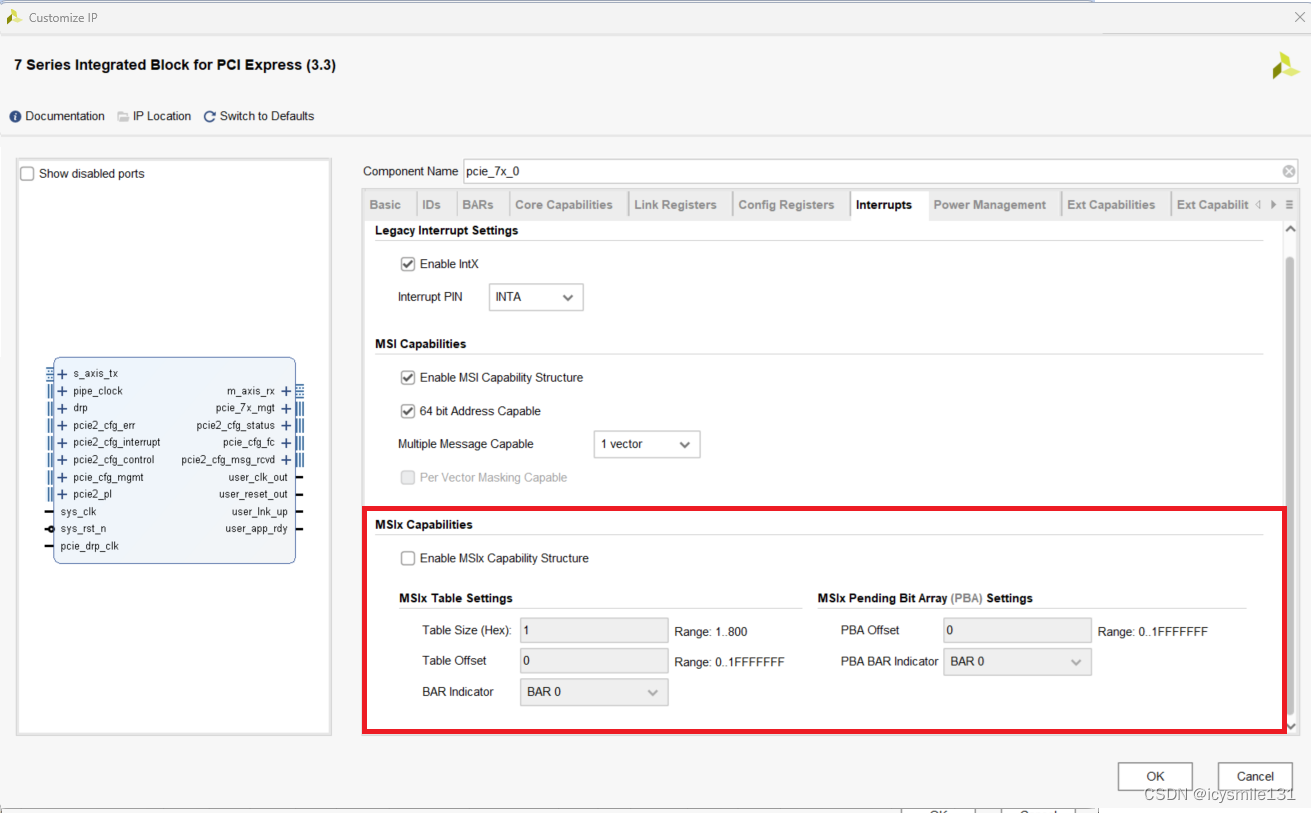

1 Interrupts选项页

在Advanced模式下显示的Interrupts参数与Basic模式中的参数类似,但会添加一些额外的参数。

MSI-X Capabilities 指的是PCI Express(PCIe)设备支持的一种中断机制,它允许PCIe设备使用MSI-X报文向处理器提交中断请求。以下是关于MSI-X Capabilities的详细解释:

- Enable MSI-X Capability Structure:当此选项被设置时,表示PCIe设备支持MSI-X中断机制,并存在MSI-X Capability结构。注意:这个能力结构至少需要配置一个Memory BAR(Base Address Register,基地址寄存器)。

- MSI-X Table Settings:定义了MSI-X表的结构。Table Size指定了MSI-X表的大小,Table Offset指定了从基地址寄存器指向MSI-X表基地址的偏移量。BAR Indicator:在配置空间中指示用于将MSI-X表映射到内存空间的基地址寄存器。对于64位基地址寄存器,这表示较低的DWORD。

- MSI-X Pending Bit Array (PBA) Settings:定义了MSI-X Pending Bit Array(PBA)的结构。PBA Offset指定了从基地址寄存器指向MSI-X PBA基地址的偏移量。PBA BAR Indicator在配置空间中指示了用于将MSI-X PBA映射到内存空间的基地址寄存器。

MSI-X中断机制与MSI中断机制相比,具有更多的优势。MSI中断机制最多只能使用32个中断向量,而MSI-X可以使用更多的中断向量,从而扩展了PCIe设备使用中断向量的个数。此外,MSI-X不需要中断控制器分配给设备的中断向量连续,解决了MSI中断机制中的这个问题。目前,Intel的许多PCIe设备都支持MSI-X中断机制。

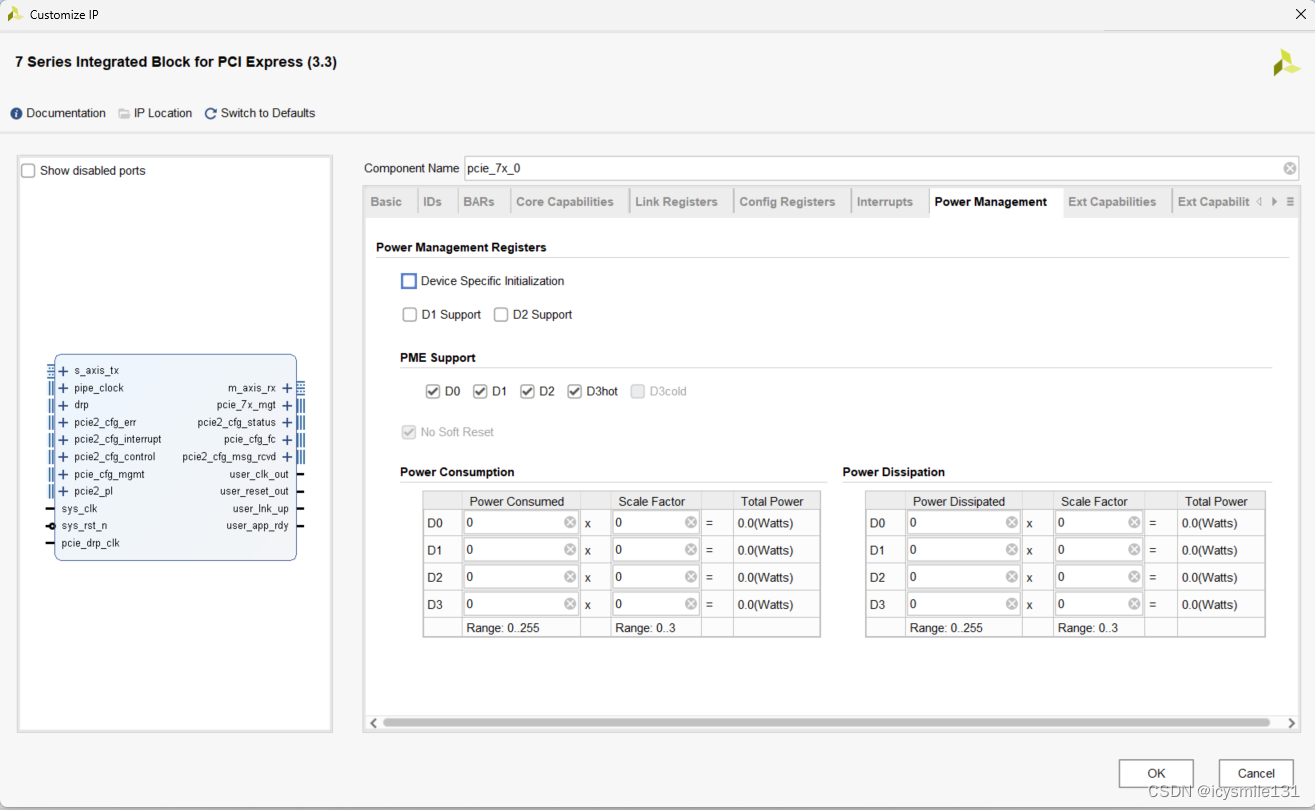

2 Power Management(电源管理)

提供了对PCIe设备的电源管理寄存器、功耗和散热选项的设置。

(1) Power Management Registers

- Device Specific Initialization:这个位指示在通用类设备驱动程序能够使用此功能之前,是否需要对它进行特殊初始化(超出标准PCI配置头之外)。当选中时,表示在转换到D0未初始化状态后,该功能需要特定的设备初始化序列。这通常用于需要特定步骤或设置来正确初始化的PCIe设备。

- D1 Support:当选中时,此选项指示该功能支持D1电源管理状态。D1是PCIe设备的低功耗状态之一,设备在此状态下仍然可以响应某些类型的请求,但功耗较低。

- D2 Support:当选中时,此选项指示该功能支持D2电源管理状态。D2是PCIe设备的另一个低功耗状态,与D1相比,设备在此状态下响应请求的能力更有限,但功耗更低。

- PME Support From:当选中时,此选项指示该功能在哪些电源状态下可以断言

cfg_pm_wake。PME(Power Management Event)是PCIe电源管理中的一个重要概念,允许设备在处于低功耗状态时向系统发送唤醒事件。通过配置此选项,您可以指定设备在哪些低功耗状态下可以触发PME事件,从而允许系统从低功耗状态恢复。 - No Soft Reset:选中此框表示,如果设备因电源状态命令从D3hot过渡到D0,则它不会执行内部重置,并且配置上下文将被保留。在某些情况下,您可能不希望设备在电源状态更改时执行内部重置,以便保留其当前配置和状态。通过选中此选项,可以实现这一功能。

(2) Power Consumption

7 Series FPGAs Integrated Block for PCI Express IP核始终报告0W的电源预算。这通常意味着该设备没有向PCI Express电源管理接口报告具体的电源需求或限制。这并不意味着设备实际上不消耗任何电能,而是说它没有遵循PCI Express电源管理规范中的特定机制来声明其电源需求。

(3)Power Dissipated

7 Series FPGAs Integrated Block for PCI Express IP核始终报告0W的电源功耗。这并不一定意味着该设备实际上不消耗任何电能。这通常是由于该集成块在PCI Express电源管理接口规范中没有明确报告其电源耗散值,或者该值在某些上下文中不被使用或不需要报告。

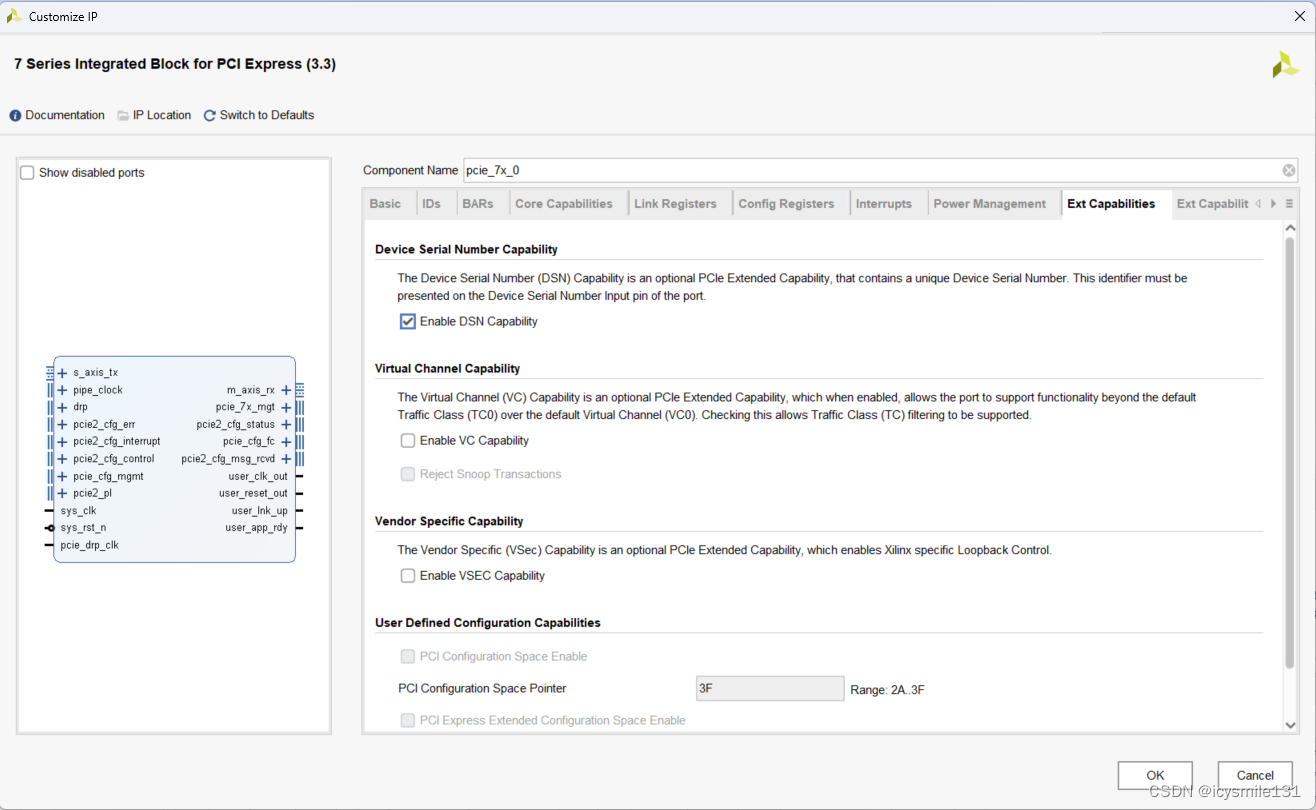

3 Extended Capabilities

在PCIe(PCI Express)规范中,扩展功能(Extended Capabilities)提供了在PCIe设备中增加额外功能的方法。通常仅在高级模式(Advanced mode)下可用。这是因为这些功能可能更加复杂,需要用户具备更深入的PCIe和设备配置知识。

(1)Device Serial Number Capability

这是一个可选的PCIe扩展功能,它包含一个唯一的设备序列号(Device Serial Number, DSN)。

Enable DSN Capability:当启用时,DSN标识符必须出现在端口的设备序列号输入引脚上。为了启用虚拟通道功能和供应商特定功能,这个功能必须被打开。

(2)Virtual Channel Capability

是一个可选的PCIe扩展功能,它允许用户应用程序在TCn/VC0模式下运行。

Enable VC Capability:当启用时,支持流量类(Traffic Class)过滤。

Reject Snoop Transactions(仅针对根端口配置):当启用时,任何适用“No Snoop”属性但未在TLP(Transaction Layer Packet)头中设置的事务都可以被拒绝为不受支持的请求。

(3)Vendor Specific Capability

是一个可选的PCIe扩展功能,允许PCI Express组件供应商公开供应商特定寄存器。

Enable VSEC Capability:当启用时,启用Xilinx特定的Loopback Control(循环回控制)。这意味着供应商(如Xilinx)可以为其PCIe设备定义自定义的功能和寄存器,以实现特定的硬件或软件优化。

(4)User-Defined Configuration Capabilities(Endpoint Configuration Only)

- PCI Configuration Space Enable:这个选项允许用户应用程序添加/实现PCI的传统功能寄存器。如果用户应用程序实现了传统的功能配置空间,应该选择这个选项。启用后,配置请求将被路由到AXI4-Stream接口,而不是内置的PCI兼容配置空间地址范围之外的地址。

- PCI Configuration Space Pointer:这个设置用于设定用户定义的PCI兼容配置空间的起始DWORD对齐地址。可用的DWORD地址范围是2Ah到3Fh。

- PCI Express Extended Configuration Space Enable:这个选项允许用户应用程序添加/实现PCIe扩展功能寄存器。如果用户应用程序实现了这样的扩展功能配置空间,应该选择这个选项。启用后,配置请求将被路由到用户应用程序,而不是内置的PCIe扩展配置空间地址范围之外的地址。

- PCI Express Extended Configuration Space Pointer:这个设置用于设定用户应用程序实现的PCIe扩展配置空间的起始DWORD对齐地址。启用后,具有大于或等于在用户应用程序中设置的值的DWORD地址的配置请求将被路由到正确的位置。可用的地址范围取决于所选的PCIe扩展功能。

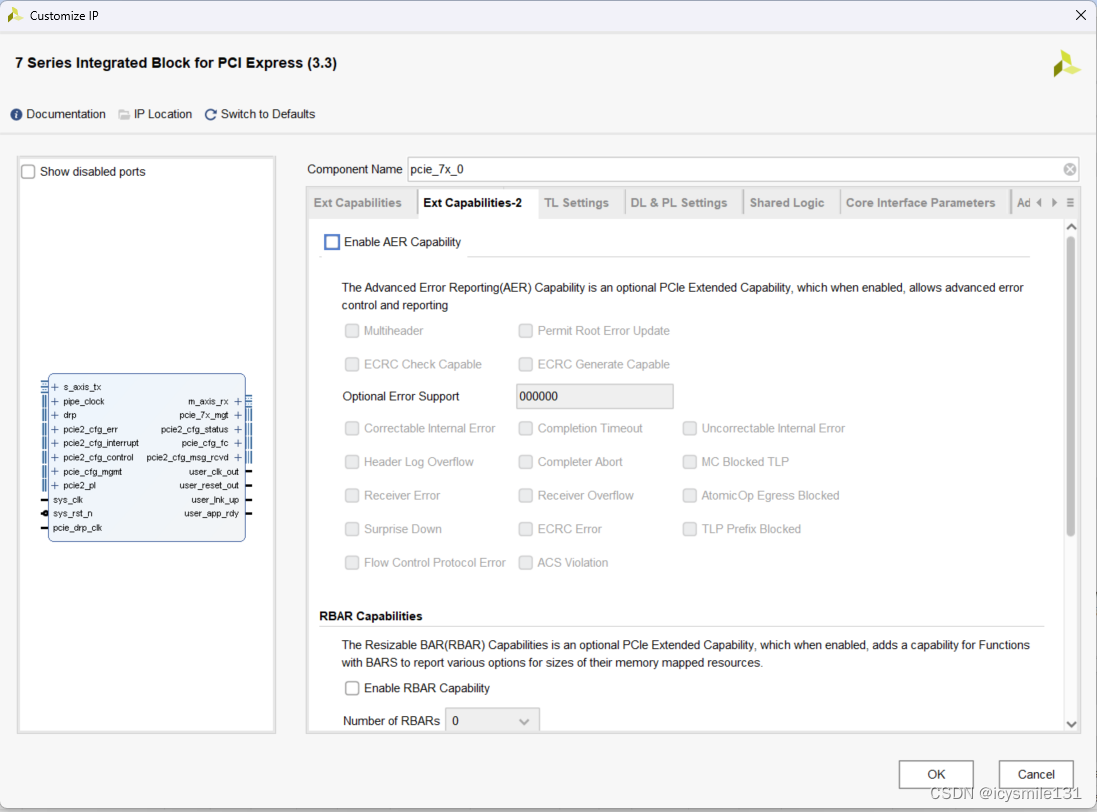

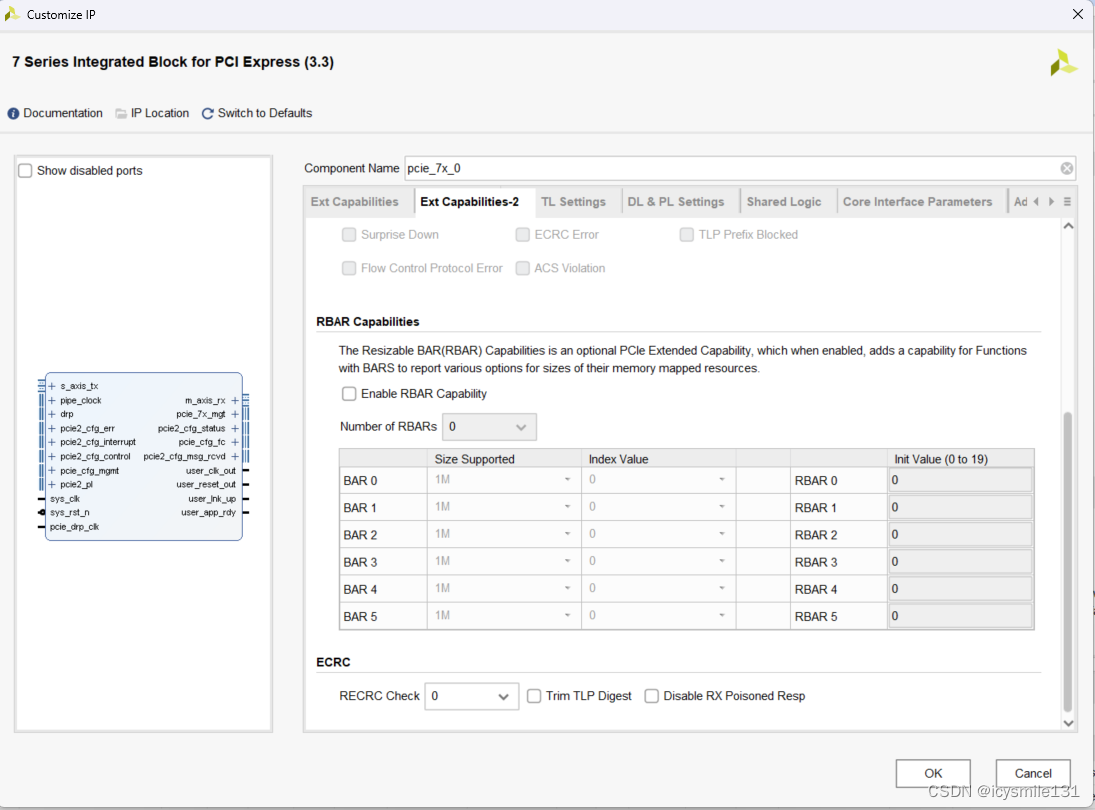

4 Extended Capabilities 2

只在Advanced模式中可用。

(1)AER Capability(高级错误报告能力)

- Enable AER Capability:允许启用AER功能,即高级错误报告。当启用后,系统可以检测和报告PCIe设备中的错误,包括不可纠正和可纠正的错误,以及传输错误、协议错误等。

- Multiheader:指示AER头日志字段是否支持多头部缓冲。然而,对于某些FPGA(如7系列FPGA)的PCIe集成块,可能不支持此功能。

- Permit Root Error Update:如果此选项设置为TRUE,则允许AER根状态和错误源ID寄存器进行更新。如果设置为FALSE,则这些寄存器将被强制置为0。

- ECRC Check Capable:指示该IP核是否能够检查ECRC(端到端循环冗余校验)。ECRC是一种用于确保PCIe设备之间数据传输完整性的技术。

- Optional Error Support:指示在不可纠正和可纠正错误掩码/严重性寄存器中支持哪些可选错误条件。如果某个错误框未被选中,则相应的掩码/严重性寄存器中的位将被硬编码为0。

(2)RBAR(Resizable Base Address Register,可调整大小的基地址寄存器)

是PCIe(PCI Express)架构中的一个可选扩展功能,它允许设备的基地址寄存器(BARs)大小是可变的。这对于那些需要动态分配内存空间的设备(如GPU)特别有用。

- Enable RBAR Capability:允许启用RBAR功能,即允许BARs的大小是可变的。当启用RBAR功能时,设备驱动程序可以动态地调整BARs的大小,以匹配设备的实际内存需求。

- Number of RBARs:指定在Cap结构中可调整大小的BARs的数量,这取决于启用的BARs的数量。每个设备可能支持不同数量的BARs,并且不是所有的BARs都需要是可调整大小的。

- BARn Size Supported:对于每个可调整大小的BAR(RBAR,其中n是BAR的索引),这个向量指定了支持的RBAR大小范围。例如,对于BAR0(即n=0),你可以指定它支持从某个最小值到某个最大值的内存大小。

- BARn Index Value:指定了从已启用的BARs中选择哪个BAR作为可调整大小的BAR。例如,如果设备有6个BARs(BAR0到BAR5),但只启用了BAR1和BAR3作为RBARs,则你需要为BAR1和BAR3分别设置BARn Index Value。

- RBARn Init Value:指定了RBAR控制BAR大小字段的初始值。当设备首次启动或重置时,BAR的大小将被设置为此初始值。之后,设备驱动程序可以动态地调整BAR的大小。

(3)ECRC(End-to-End CRC,端到端循环冗余校验)

是一种在PCI Express(PCIe)系统中用于检测事务层包(Transaction Layer Packets, TLPs)在端到端传输过程中可能发生的错误的机制。

-

ECRC Check:用于启用或禁用接收到的TLPs的ECRC检查。如果设置为0,系统不会检查ECRC。如果设置为1,系统总是检查ECRC。如果设置为3,系统会根据AER(Advanced Error Reporting)功能结构中的ECRC检查启用位来决定是否检查ECRC。

-

Trim TLP Digest:允许系统在接收到的TLPs上启用TD位清除和ECRC修剪。具体的实现和效果可能依赖于具体的PCIe设备和驱动程序。

-

Disable RX Poisoned Resp:用于禁用由于接收到被污染(Poisoned)的TLPs而导致的IP核发送消息和设置状态位的行为。当启用时(设置为TRUE),如果接收到被污染的CfgWr(配置写操作),IP核会设置Parity Error并发送带有UR(Unsupported Request)的完成消息。如果接收到被污染的MemWr(内存写操作),IP核会设置Parity Error但不发送任何TLP。

如果在Advisory Non-Fatal Error Mask被设置为0的情况下,并且DISABLE_RX_POISONED_RESP被设置为FALSE,当接收到被污染的MemWr时,IP核会自动发送错误消息。如果DISABLE_RX_POISONED_RESP被设置为TRUE,则不会发送错误消息。

当cfg_err_poisoned被断言时,无论DISABLE_RX_POISONED_RESP的设置如何,核心都会发送错误消息。