实验目的:

1、使用铆孔U7输出一个脉冲,频率不定。

2、使用铆孔V7测量脉冲频率,并在数码管上显示。

实验内容及步骤:

- 设计原理

测量频率的方法有很多,按照其工作原理分为无源测量法、比较法、示波器法和计数法等。计数法在实质上属于比较法,其中最常用的方法是电子计数器法。电子计数器是一种最常见、最基本的数字化测量仪器。

数字计数式频率计能直接计数单位时间内被测信号的脉冲数,然后以数字形式显示频率值。这种方法测量精确度高、快速,适合不同频率、不同精确度测频的需要。电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法,如周期测频法。

由于数字电路的飞速发展和集成电路的普及,计数器的应用十分广泛。利用电子计数器测量频率具有精度高,显示醒目直观,测量迅速,以及便于实现测量过程自动化等一系列突出优点,所以该方法是目前最好的。

1.任务分析

数字频率计是采用数字电路制做成的能实现对周期性变化信号频率测量的仪器。频率计主要用于测量正弦波、矩形波、三角波和尖脉冲等周期信号的频率值。其扩展功能可以测量信号的周期和脉冲宽度。通常说的,数字频率计是指电子计数式频率计。

被测输入信号:方波

测试频率范围:0HZ-48MHZ

显示方式:用8个BCD七段数码管显示读数。采用对高为无意义补零显示。

3.模块设计

闸门产生、闸门电路工作原理:在测试电路中设置一个闸门产生电路,用于产生脉冲宽度为1s的闸门信号。该闸门信号控制闸门电路的导通与开断。让被测信号送入闸门电路,当1s闸门脉冲到来时闸门导通,被测信号通过闸门并到达后面的计数电路(计数电路用以计算被测输入信号的周期数),当1s闸门结束时,闸门再次关闭,此时计数器记录的周期个数为1s内被测信号的周期个数,即为被测信号的频率。测量频率的误差与闸门信号的精度直接相关,因此,为保证在1s内被测信号的周期量误差在10³量级,则要求闸门信号的精度为10 ⁴量级。例如,当被测信号为1kHz时,在1s的闸门脉冲期间计数器将计数1000次,由于闸门脉冲精度为10⁴,闸门信号的误差不大于0.1s,固由此造成的计数误差不会超过1,符合5*10³的误差要求。进一步分析可知,当被测信号频率增高时,在闸门脉冲精度不变的情况下,计数器误差的绝对值会增大,但是相对误差仍在5*10³范围内。

闸门信号产生、闸门电路实现方法

方法一:通常上述电路可以用分频器产生和多路选择器实现

方法二:采用相位累加法精确控制闸门

代码如下:

//

//8位数码管显示控制模块smg

//module smg(clk, d1, d2, d3, d4, d5, d6, d7, d8, sel, seg);

input clk;

output reg [7:0] sel;

output reg [7:0] seg; //a~g,dp

input [3:0] d1, d2, d3, d4; //d[7]-dp, d[6:0]-ASCII

input [3:0] d5, d6, d7, d8; //d[7]-dp, d[6:0]-ASCII //扫描频率:50Hz

parameter update_interval = 48000000 / 400 - 1;

reg [4:0] dat;

reg [2:0] cursel;

integer selcnt;//扫描计数,选择位

always @(posedge clk)

beginselcnt <= selcnt + 1;if (selcnt == update_interval)beginselcnt <= 0;cursel <= cursel + 1'b1;end

end//切换扫描位选线和数据

always @(posedge clk)

begincase (cursel)3'b000: begin dat = d1; sel = ~8'b00000001; end3'b001: begin dat = d2; sel = ~8'b00000010;end3'b010: begin dat = d3; sel = ~8'b00000100; end3'b011: begin dat = d4; sel = ~8'b00001000; end3'b100: begin dat = d5; sel = ~8'b00010000; end3'b101: begin dat = d6; sel = ~8'b00100000;end3'b110: begin dat = d7; sel = ~8'b01000000; end3'b111: begin dat = d8; sel = ~8'b10000000; endendcase

end//更新段码

always @(posedge clk)

beginseg[0] <= dat[4]; //dpcase (dat[3:0])4'h00 : seg[7:1] <= ~7'b0000001; //04'h01 : seg[7:1] <= ~7'b1001111; //14'h02 : seg[7:1] <= ~7'b0010010; //24'h03 : seg[7:1] <= ~7'b0000110; //34'h04 : seg[7:1] <= ~7'b1001100; //44'h05 : seg[7:1] <= ~7'b0100100; //54'h06 : seg[7:1] <= ~7'b0100000; //64'h07 : seg[7:1] <= ~7'b0001111; //74'h08 : seg[7:1] <= ~7'b0000000; //84'h09 : seg[7:1] <= ~7'b0000100; //9 4'h0a : seg[7:1] <= ~7'b0001000; //a 4'h0b : seg[7:1] <= ~7'b1100000; //b 4'h0c : seg[7:1] <= ~7'b1110010; //c 4'h0d : seg[7:1] <= ~7'b1000010; //d 4'h0e : seg[7:1] <= ~7'b0110000; //e 4'h0f : seg[7:1] <= ~7'b0111000; //f default : seg[7:1] <= ~7'b0110000; //E-rrorendcase

endendmodule

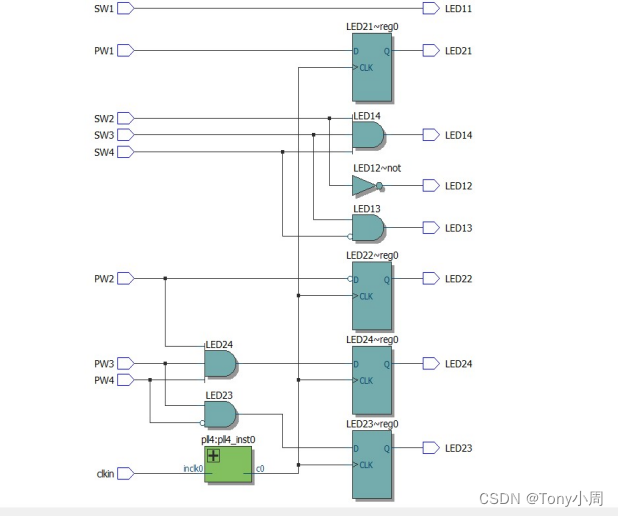

module freqmeasure(output P99,//输出脉冲 input P100,//测量脉冲 output [7:0] sel,output [7:0] seg, //a~g,dpinput clkin//时钟);//

//

//锁相环模块

//

//

wire clk;

pll4 pll4_inst0(.inclk0(clkin),//12Mhz.c0(clk)//48Mhz

);reg [31:0] count;

reg clk_1s;

//1S定时时钟产生

always @(posedge clk )

beginif(count<48_000_000-1)begincount <= count+1;clk_1s <= 0;endelse begincount <= 0;clk_1s <= 1; end

end reg [31:0] count_p100;

always @(posedge P100 ) count_p100 <= count_p100+1;reg [31:0] count_p100_last;

reg [31:0] freq_1s;

always @(posedge clk )

if(clk_1s)

beginfreq_1s <= count_p100-count_p100_last;count_p100_last <= count_p100;

endreg [31:0] phase;

always @(posedge clk )

phase <= phase + 123456789;assign P99 = phase[31]; //freq=48000000*123456789/2^32//

//

//数码管模块

//

//

smg smg_inst

(.clk(clk) , // input clkin.d1(d1) , // input [4:0] d1.d2(d2) , // input [4:0] d2.d3(d3) , // input [4:0] d2.d4(d4) , // input [4:0] d2.d5(d5) , // input [4:0] d2.d6(d6) , // input [4:0] d2.d7(d7) , // input [4:0] d2.d8(d8) , // input [4:0] d2.sel(sel) , // output [7:0] sel.seg(seg) // output [7:0] seg

);reg [3:0] d1, d2 ; //d[4]-dp, d[3:0] reg [3:0] d3, d4 ; //d[4]-dp, d[3:0] reg [3:0] d5, d6 ; //d[4]-dp, d[3:0] reg [3:0] d7, d8 ; //d[4]-dp, d[3:0]

reg [7:0]status;reg [31:0]s,s1,div;always @(posedge clk)

begins1<=freq_1s/div;s<=s1%10;status <= status+1;

case(status[7:4])

0:div<=10000000;

1:d1 <= s;2:div<=1000000;

3:d2 <= s;4:div<=100000;

5:d3 <= s;6:div<=10000;

7:d4 <= s;8:div<=1000;

9:d5 <= s;10:div<=100;

11:d6 <= s;12:div<=10;

13:d7 <= s;14:div<=1;

15:d8 <= s;endcase

end

endmodule

module freqmeasure(

output P99,//输出脉冲

input P100,//测量脉冲

output [7:0] sel,

output [7:0] seg, //a~g,dp

input clkin//时钟

);

//

//

//锁相环模块

//

//

wire clk;

pll4 pll4_inst0(

.inclk0(clkin),//12Mhz

.c0(clk)//48Mhz

);