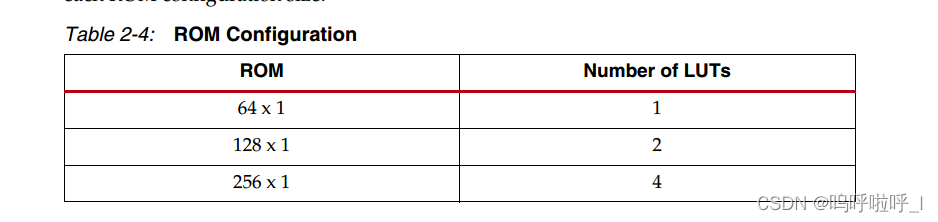

1.首先说SliceM和SliceL如何配置为ROM的

一个SLICE包含4个六输入查找表,因此每个查找表就能存储64bit的数据,要实现128bit的ROM,只需要通过两个LUT就可实现,具体如下表:

2.如何配置成为分布式RAM

SLICEM中的LUT如下图:

DI为输入的数据,WCLK为同步时钟,WE为使能信号,A[5:0]为地址总线、WA为写数据总线,LUT的输出Output是异步读取结果,输出端可选是否使用寄存器实现同步读。

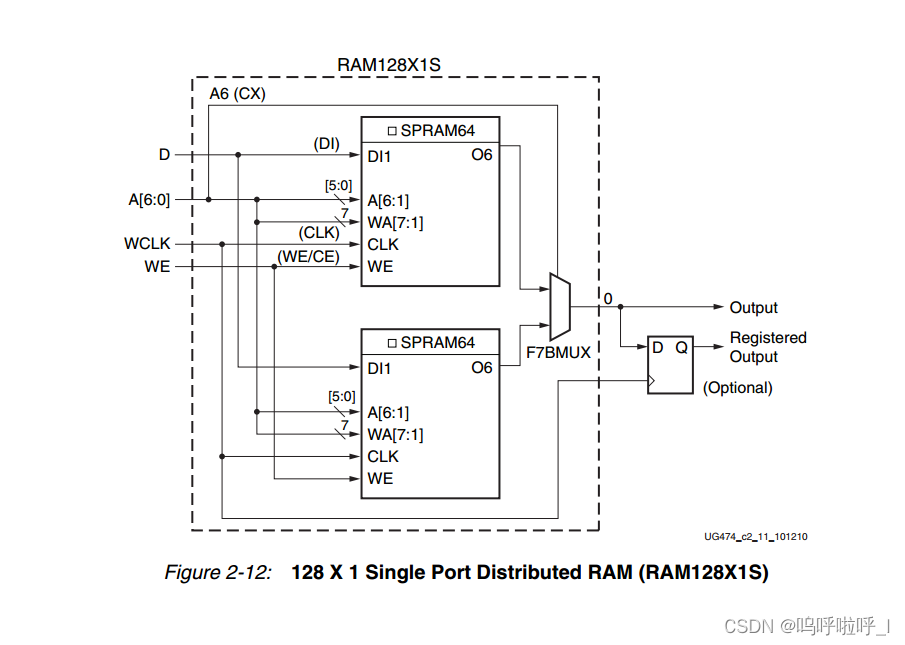

(1)128×1的单口RAM

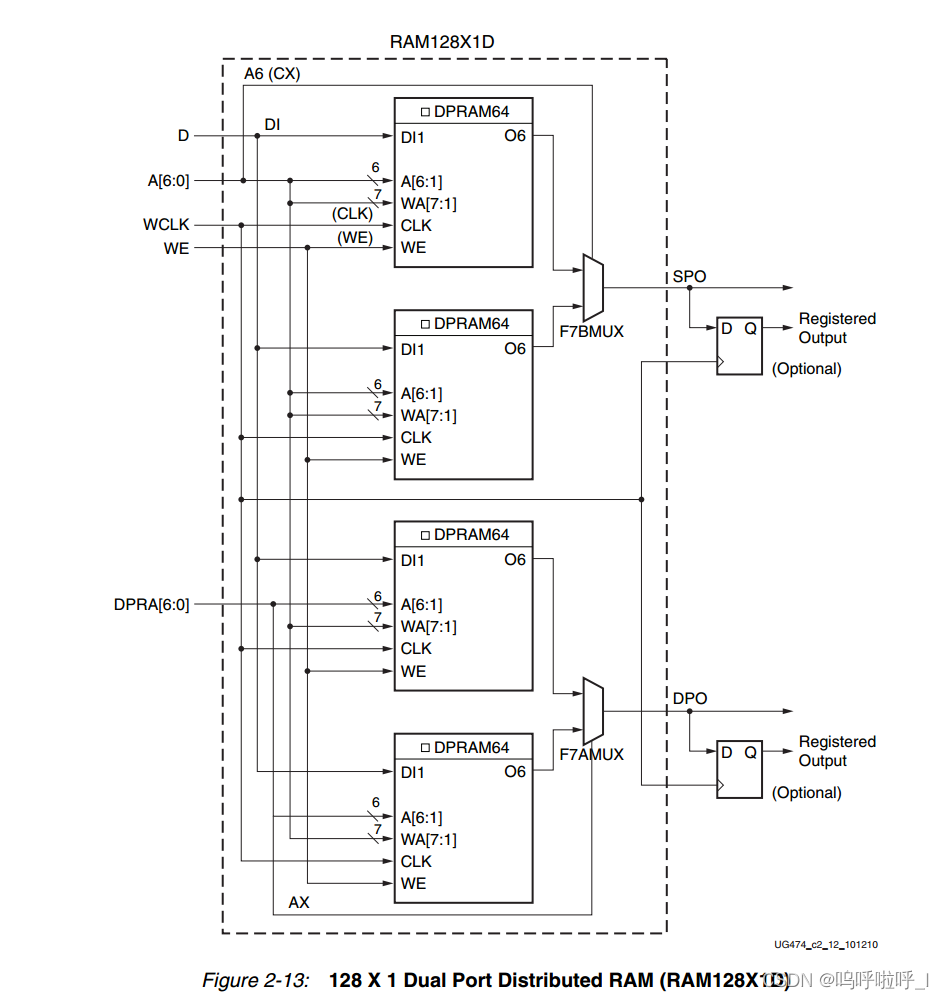

(2)128×1的双口RAM

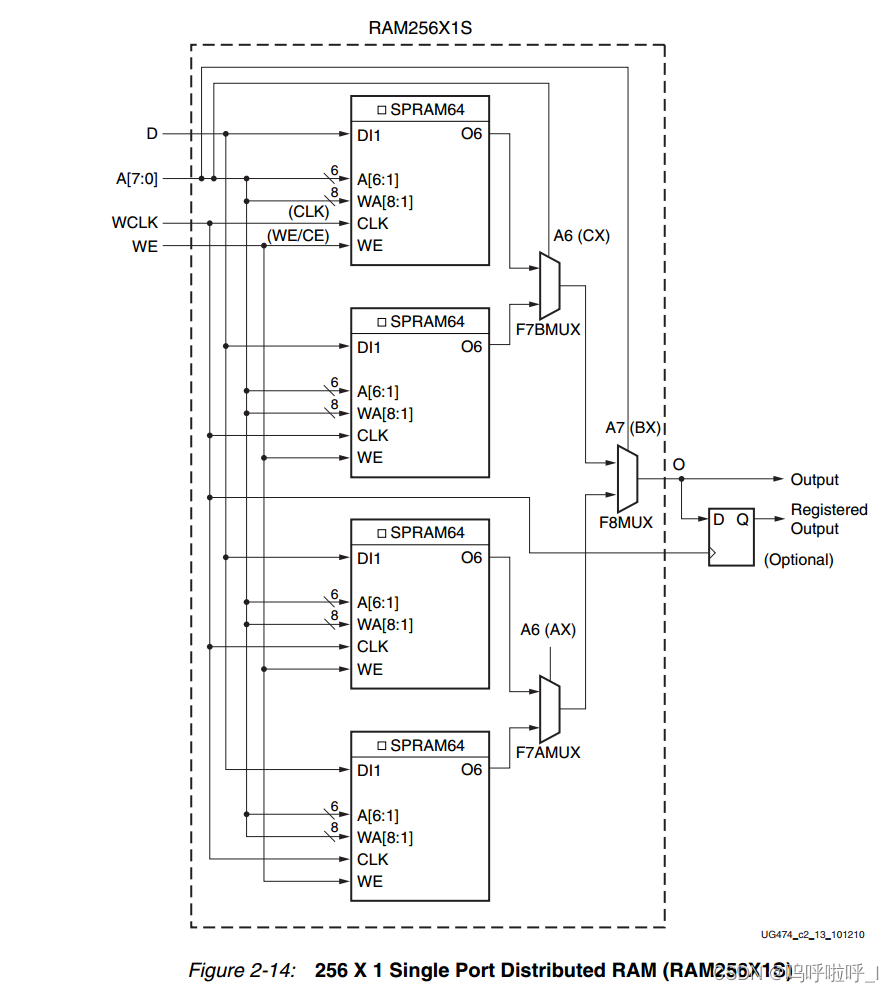

(3)256×1的单口RAM

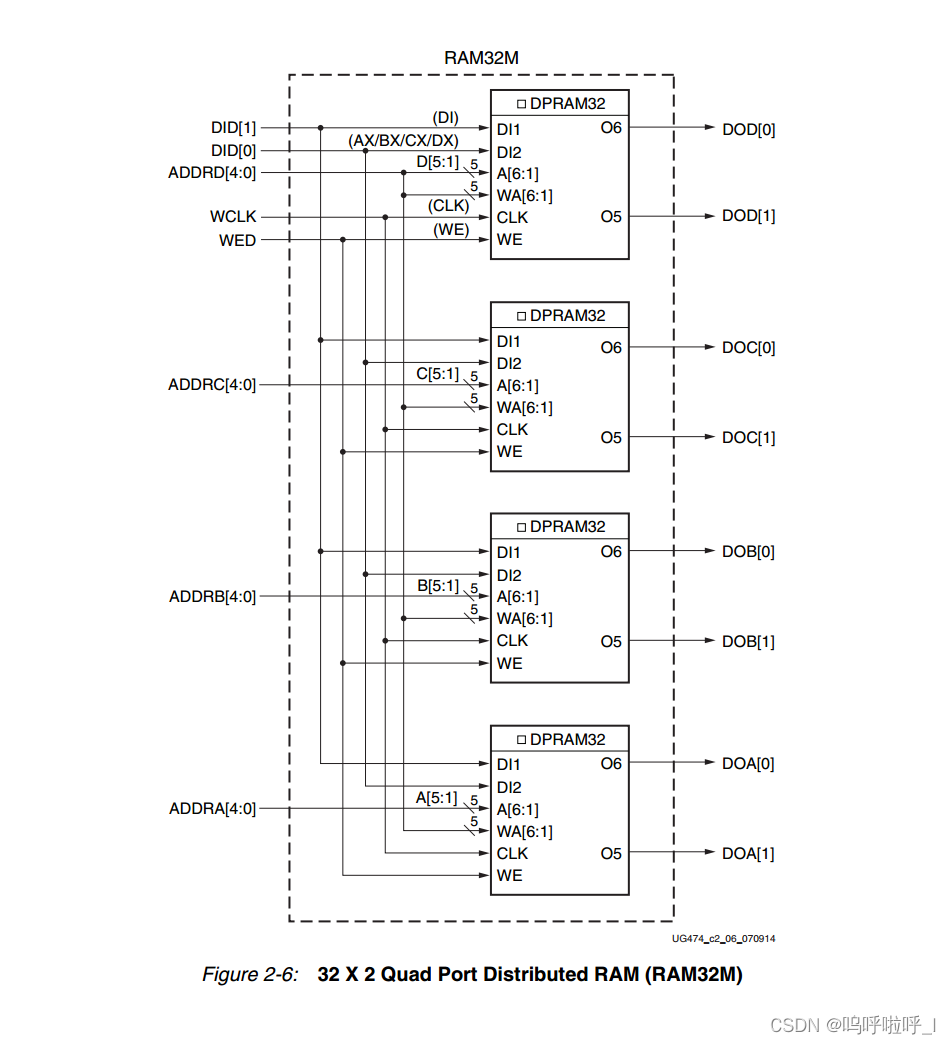

(4)32×2的四端口RAM

除了上述的方式,还可以将其当作两个5输入LUT,例如下图将其配置成32*2的四端口,这时候可以发现一个LUT其实只有32位深度,正式因为采用了5输入LUT的方式(1个6输入LUT中的两个5输入LUT分别配置成宽度位1bit、深度为32的RAM,公用一组地址线、写使能,写数据输入分别为DI1和DI2)。

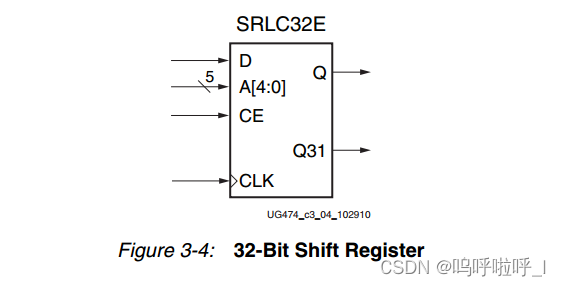

3.如何配成成为移位寄存器

SILCEM相比SLICEL之所以能够配置成移位寄存器,是因为其LUT具有写数据端(DI1 DI2),写地址线(WA1-WA8),写使能端(WE),而SLICEL的LUT6没有。这样就可以将外部的数据输入进来,实现32位移位寄存器。

时序图如下:

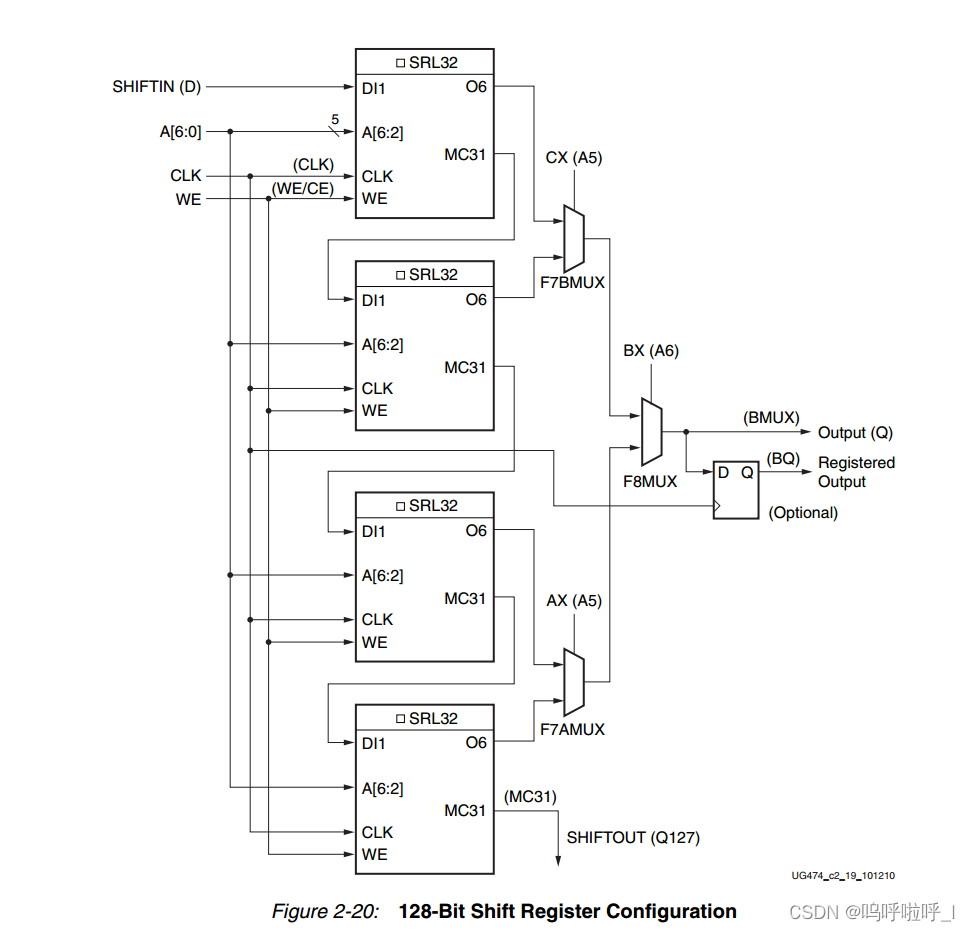

如果要实现64/96/128移位寄存器,可以通过级联的方式实现。

但是如果希望设计的移位寄存器并不是32位或者32位的倍数呢?

任何32位都可以通过改变地址异步读出(在O6 LUT输出,在原语中称为Q),此功能在创建较小的移位寄存器(小于32位)时非常有用。例如,当构建一个13位移位寄存器时,将读地址设置为第13位对应的地址即5'b1101,这时候输出可以选择Output(Q)或者Registered Output,可以实现同步获取移位寄存器输出。(LUT的读是异步的)

4.与LUT相关的原语

(1)多路复用器

| 原语 | 输入 | 资源 | 功能 |

| MUXF7 | 两个LUT的输出 | F7AMUX/F7BMUX | 8选1选择器 |

| MUXF8 | F7AMUX/F7BMUX的输出 | F8MUX | 16选1选择器 |

两种多路复用器的端口相同,如下:

- 数据输入端:I0,I1

- 控制信号:S

- 数据输出:O

问题:为何无论是8选1还是16选一,其输入都只有两个数?这样不是二选一吗?

实际上要明白这个需要联系上文中如何实现这些功能的。在上文的介绍中,MUXF7的输入是两个LUT的输出结果,这时相当于是二选一,而LUT又是一个4选1的选择器,因此实现了8选1的功能。

MUXF8实现16选1是在MUXF7的基础上,再对相邻的MUXF7/MUXF8的输出再进行选择,实现16选1的输出。

使用原语的例子如下:

MUXF7 MUXF7_inst (

.O(O), // Output of MUX to general routing

.I0(I0), // Input (tie to LUT6 O6 pin)

.I1(I1), // Input (tie to LUT6 O6 pin)

.S(S) // Input select to MUX

);MUXF8 MUXF8_inst (

.O(O), // Output of MUX to general routing

.I0(I0), // Input (tie to MUXF7 L/LO out)

.I1(I1), // Input (tie to MUXF7 L/LO out)

.S(S) // Input select to MUX

);

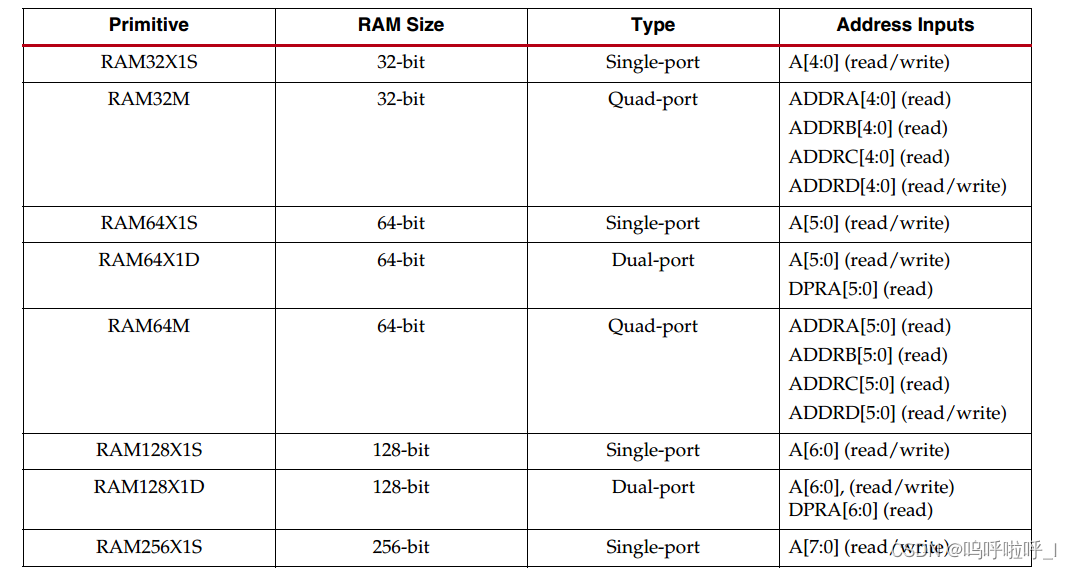

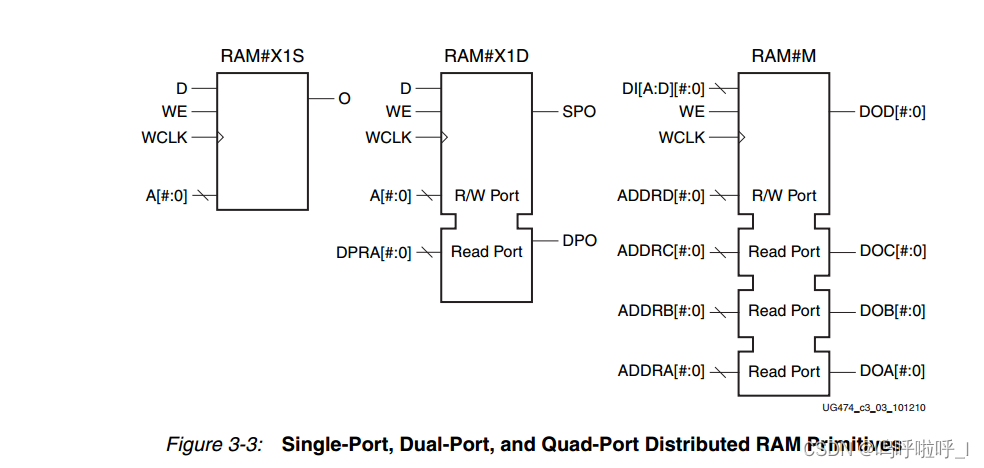

(2)分布式RAM

- D:数据输入端

- WE:写使能

- WCLK:写时钟

- A[#:0]:地址

- O:移位输出

以32×1的单端口RAM为例:

RAM32X1S_1 #(.INIT(32'h00000000) // Initial contents of RAM)RAM32X1S_1_inst (.O(O), // RAM output.A0(A0), // RAM address[0] input.A1(A1), // RAM address[1] input.A2(A2), // RAM address[2] input.A3(A3), // RAM address[3] input.A4(A4), // RAM address[4] input.D(D), // RAM data input.WCLK(WCLK), // Write clock input.WE(WE) // Write enable input);更多原语可按照下面这边文章里的步骤找到如何例化:

Xinlinx原语在哪查看如何使用/原语示例-CSDN博客

(3)移位寄存器

SRLC32E #(.INIT(32'h00000000) // Initial Value of Shift Register) SRLC32E_inst (.Q(Q), // SRL data output.Q31(Q31), // SRL cascade output pin.A(A), // 5-bit shift depth select input.CE(CE), // Clock enable input.CLK(CLK), // Clock input.D(D) // SRL data input);

Xinlinx官方CLB文档如下:

7 Series FPGAs Configurable Logic Block User Guide (UG474) • 查看器 • AMD 技术信息门户