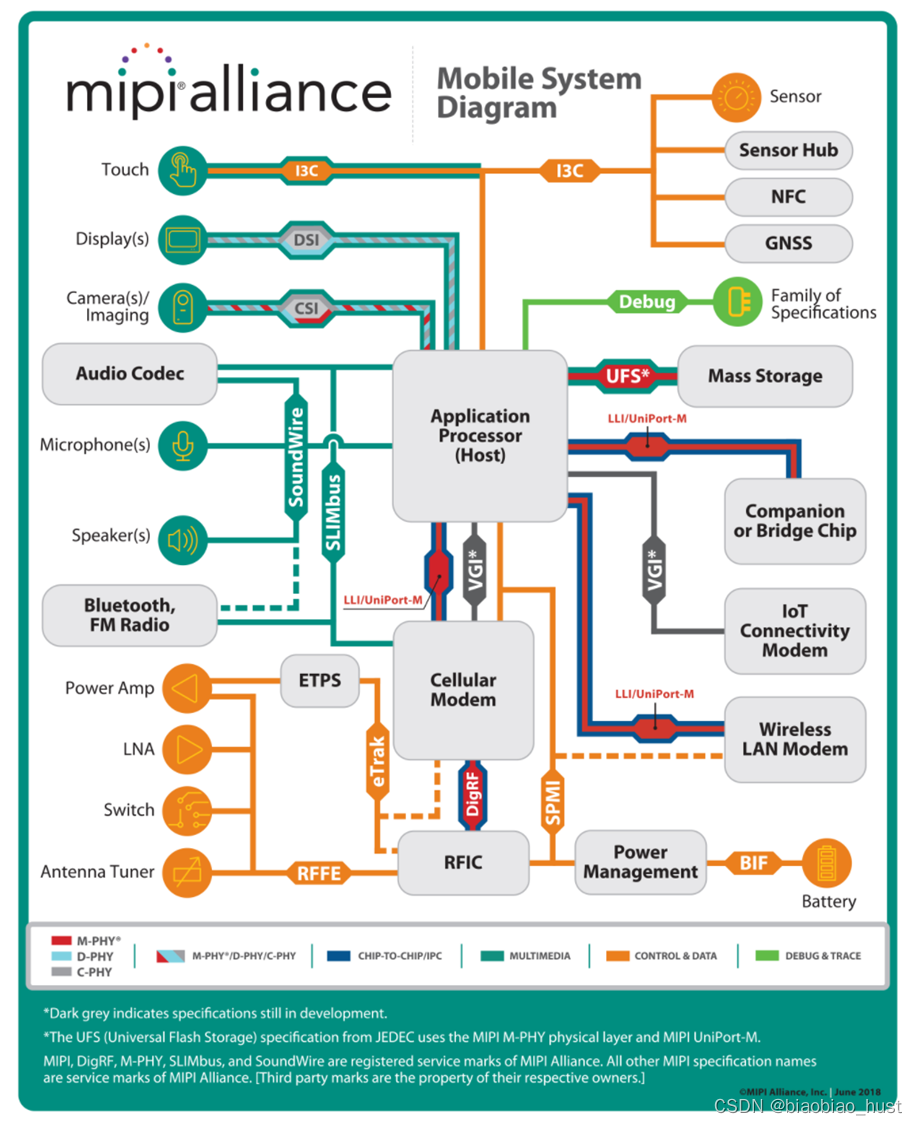

1. 概况

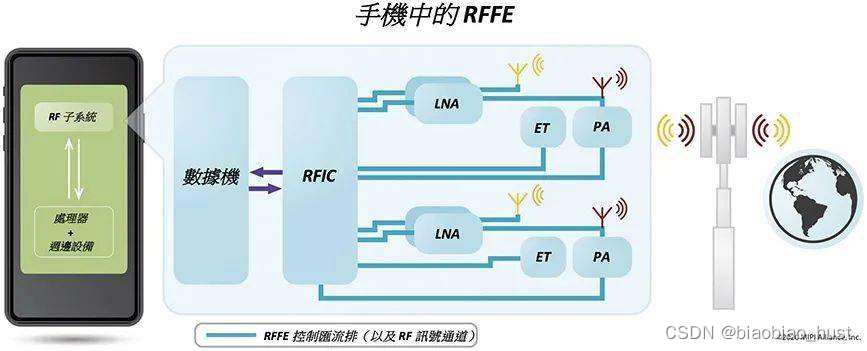

MIPI RFFE是一种专门针对当前及未来无线系统在射频(RF)前端控制界面规范。随着手机射频系统日趋复杂,业界需要一个单一控制界面解决方案。MIPI联盟的RF前端控制界面(RFFE)规范通过提供一个可连接到收发器或无线电的总线界面解决了这一难题,可用于给多种射频前端设备,如低噪声放大器(LNA)、功率放大器(PA)、天线开关、天线调谐器、DC/DC转换器、滤波器、感测器等。

对5G而言,几乎没有什么比RF前端(RFFE)控制基础架构更为重要。任何影片数据、任何应用程序数据(基本上以无线方式传输或接收的任何内容皆然)都仰赖RFFE来控制RF前端模块(FEM)或子系统,包含所有功率放大器、天线调谐器、滤波器、低噪声放大器(LNA)、交换器等等,这些子系统均链接至调制解调器基频和/或射频集成电路(RFIC)收发机。

MIPI RFFE(MIPI RF Front-end,MIPI射频前端)是MIPI联盟RFFE工作组在2010年推出的用于移动终端射频前端控制的控制接口标准。MIPI RFFE协议总线由一根电源线(VIO)以及两根控制线(SCLK和SDATA)共3根线构成,实现简单,易于部署,可实现时序范围要求内的近实时控制。

在MIPI RFFE推出之前,射频前端的控制解决方案复杂,如果用并行的GPIO口进行控制,需要接口过多,系统成本无法承载;一些厂商开始自定义串口控制,不过由于通信协议复杂,需要考虑复杂的软件控制和时序控制,实现困难,并且自定义串口也不利于不同厂商器件的通信。

目前,MIPI协议已演进至V3.0版本,支持多种Trigger模式,适应5G通信系统中更多器件以及更严苛的时序控制要求。各个MIPI版本演进时增加的主要特性如下:

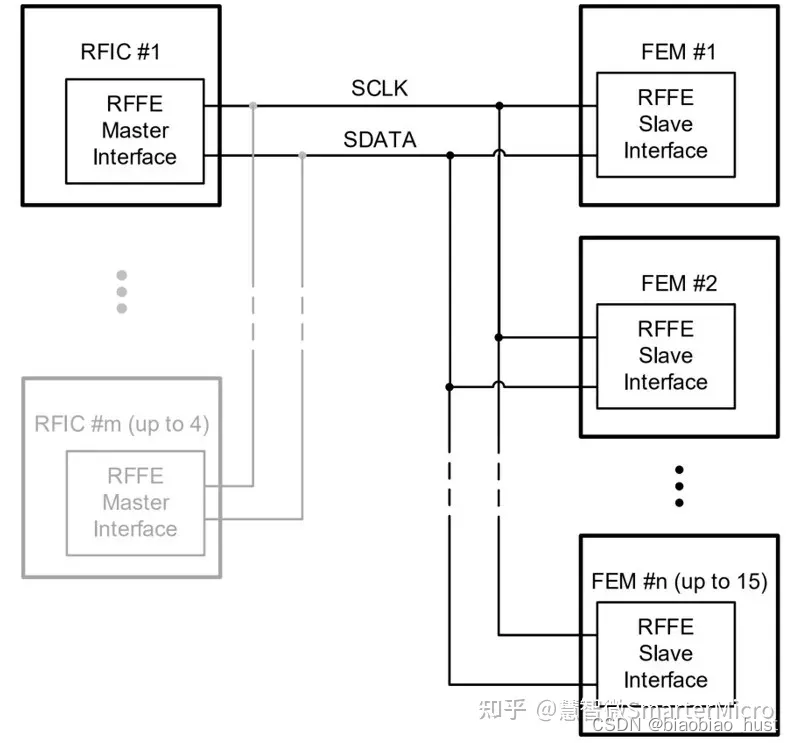

2. MIPI RFFE的系统架构

一个MIPI RFFE的架构通常包含:

-

Signal Bus:包含SCLK和SDATA两条信号线

-

RFFE Master Device:控制系统MIPI signal bus的器件,一般为手机系统中的RFIC(transceiver),单个MIPI系统最多可支持4个Master device

-

BOM:Bus Own Master,任一时刻只能有一个BOM被激活

-

RFFE Slave Device:MIPI受控器件,一般为射频前端模组,例如PA、LNA、Switch等,单个MIPI系统最多可支持15个device

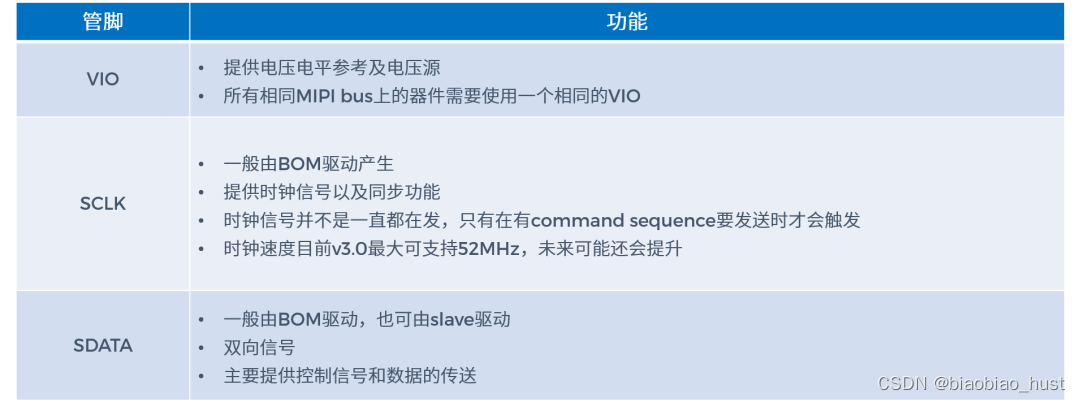

一个Slave器件的MIPI管脚除了SCLK和SDATA还有一个VIO,这些管脚功能如下表:

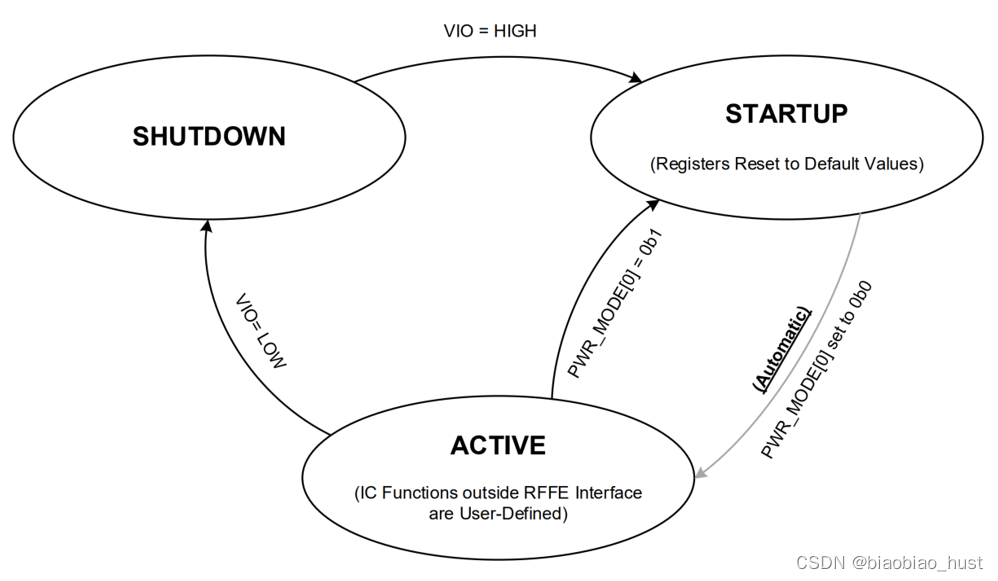

一个Slave器件会有三种状态,分别为Active、Shutdown和Startup。

-

VIO控制MIPI系统是否Shutdown

-

当VIO=high时,MIPI进入Startup状态,随后自动进入active状态

-

如需对MIPI寄存器进行重置,可发1C寄存器中PWR_MODE[0]=0b1

3. MIPI RFFE控制指令

MIPI通信主要通过控制Slave器件的相关寄存器,以达到控制器件的目的。在MIPI RFFE协议中定义了多种寄存器,寄存器包含:

-

系统定义寄存器:系统规定有特殊应用的寄存器,如上文所提到的1C寄存器有PWR_MODE控制等

-

用户定义寄存器:用户可根据具体应用定义寄存器功能

一个操作的控制指令基本会包含以下几部分:

-

SSC(Sequence Start Condition):指令开始标志

-

Command Frame:一般包含SA(Slave Address)、操作类型对应代码、以及奇偶校验码

-

Data Frame:不一定有,同时也包含奇偶校验码

-

BPC(Bus Park Cycle):指令结束标志

3.1 MIPI RFFE传输

两个模块要信息交换,(我们称行动的发起方为master,信息的接收方为slave),那肯定有约定,不然它们是不知道谁跟谁在交流,也不知道信息什么时候开始,什么时候结束。那对于RFFE,它采用的沟通方式从大的方面来说就两种:

a.读命令+读地址;

b.写命令+写地址+写数据。

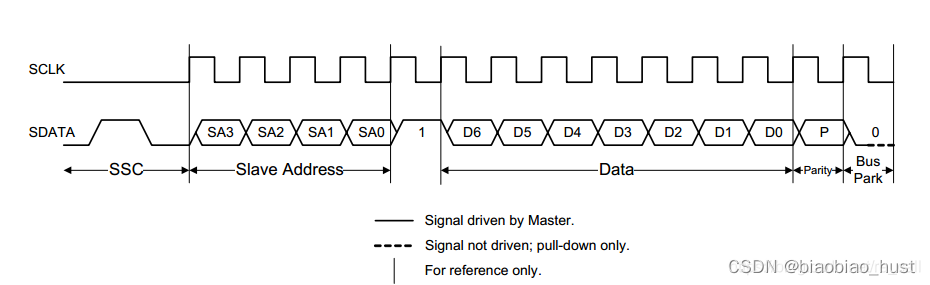

以Register 0 write command 为例。Register 0 write command是一个特殊的命令,它的作用是只写slave的地址为0的寄存器。为什么slave寄存器0单独开一个命令呢?我想可能是因为一般模块的关键控制开关都放在寄存器0中,人们希望发最少的数据就可以控制slave,那么就单独为寄存器0开设一个命令了。如果了解了其他命令,我们知道这可以用一般的写命令来达到同样效果的。该命令的时序如下:

从上面时序图中,我们可以看到:

- RFFE接口只有两根线,一根是时钟线,一根是数据线。

- 图中注释的SSC,sequence start condition,表示命令开始。我们SSC其实就是一个CLK,按照协议的说法,这个高电平要持续一个内部时钟周期,低电平也要持续一个内部时钟周期。但是我在设计时,高低电平分别持续了SCLK一个周期,发现也可以正常工作的。这个SSC是关键点,如果设计不对,命令下发肯定要失败的。

- 时序中的SA3-SA0表示slave的ID信息。

- D6-D0就是要想寄存器0写的数据。

- Parity就是前面的SA,1,data的奇偶校验信息。RFFE中采用的是奇校验,即加上奇偶校验位,一帧中包含的1的个数为奇数。

- Bus Park标志着该帧命令的结束。就像SSC作为帧命令的开始一样,帧结束并不是用指令来表示的,而是用时钟线和数据线的组合来表示的。在发送完一帧的奇偶校验位后,数据线要拉到低电平并保持半个SCLK周期,然后master要让出数据线权限。SCLK要再发一个时钟。

- 数据线SDATA是一个双向接口。在master向slave写时,master占有SDATA权限。当写的信息完成时,要释放SDATA权限,这种占有和释放时,通过三态门实现的,我们只要输出一根使能信号就好。如下图中的SDATA_EN在master向slave写数据时要为高电平。注意图中SDATA_EN拉高的起始点和拉低的接收点。开始点是与SSC一起的,结束点在Bus park的前半周期后。

4. MIPI ID配置

MIPI RFFE中定义了多种ID,ID作为MIPI中Slave器件的识别代号有着非常重要的作用。

-

MID(Manufacturer ID):每个厂商在加入MIPI Alliance之后都会被分配一个专门的MID,可以从官网(https://mid.mipi.org/)查询到,例如慧智微电子分配到的MID为:2E9(hex)

-

PID(Product ID):由厂商自行管理给不同产品配置不同的PID,在MIPI RFFE V2.1引入了Extend-PID,这样PID就包含16bits供配置

-

USID(Unique Slave ID):MIPI bus主要通过USID对Slave器件进行寻址,USID共4bits 16组状态,但一个MIPI bus上最多15个Slave器件,MIPI RFFE定义SID=0b0000时为广播ID,即BSID(Broadcast Slave ID)

MID和PID所对应的寄存器都是read-only,而USID一般有一个默认的值,同时可以支持可编程。原因是MIPI指令是以USID进行寻址的,当一个MIPI bus上的所有Slave器件存在两个或以上的USID是相同的时候,会导致无法区分,因此可编程的USID至关重要。

更新USID的步骤流程为:

- 通过当前USID写入PID寄存器(0x1D),写入值需要和想要更新器件的PID值相同

- 通过当前USID写入MID寄存器(0x1E), 写入值需要和想要更新器件的MID值相同

- 通过当前USID写入USID寄存器(0x1F),写入要新的USID值,当写入PID/MID与想要更新的器件PID/MID值一致时,新的USID值即生效,反之USID仍维持原来的值

简单来讲就是只有当MID/PID以及默认USID对应上之后才能够对USID进行更新,这就要求:当一个MIPI bus上挂有多个相同产品(MID/PID相同)时,为了做可编程的区分,一般会在此产品增加ID pin脚,其接高电平或GND分别对应不同的默认USID。

5. MIPI RFFE Trigger模式

5G将带来涉及上行和下行通讯的RF频带数量的爆炸性成长,并相应缩小RF封包间的子载波间距(SCS)。另一项不断发展的需求,则是要缩短在各频段和频段组合间切换的延迟时间。传统上RFFE主要是部署在手机中,但随着5G的推出,无线通信的控制需求也扩展到汽车、物联网和其他使用案例上,这也影响了现况。有鉴于此,开发MIPI RFFE v3.0的目的在于让使用案例不仅局限于行动设备,并针对当今3GPP 5G标准中定义的更高计时精准度和更短延迟时间,满足一些前所未有的需求。

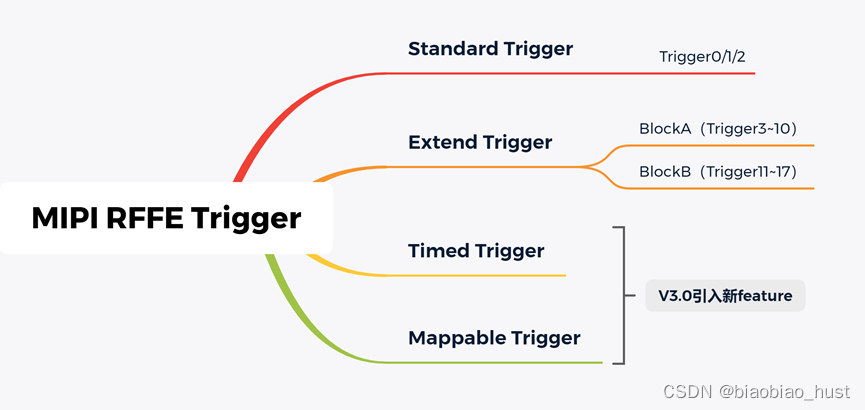

为了因应5G的需求,在更短时间内完成动态配置更改,最新推出的v3.0为接口的触发器提供了多项增强措施。为了实现更快的控制速度,MIPI RFFE V2.0中将时钟速度由26MHz提升至52MHz,采用52MHz通信后,单个寄存器件读写的时间减少一半。但这还不足以满足5G通信系统的时序要求。为此,MIPI V3.0中着重升级了Trigger模式功能。不仅Trigger的数量由V1.0的3个、V2.1中的11个,增加至V3.0中的18个,而且还增加了Timed Trigger和Mappable Trigger功能。各种触发器可用于让RF子系统能够在极严时间控制下配置多部RF设备,以及在一部从属设备内或跨多部设备间同步缓存器设定变更。

5.1 Trigger功能的引入

当要控制一个射频芯片时,可能需要写入多个寄存器,通常可以按照串行方式每个寄存器轮流写入及生效,但由于每个寄存器生效存在时间差(以52MHz为例,每个寄存器写入时间为~0.5μs),这期间可能导致芯片工作不正常。为了解决这个问题,MIPI协议中针对UDR寄存器引入的Trigger模式,即通过Trigger功能,触发多个寄存器同时生效。

Trigger作为MIPI RFFE的重要Feature,随着5G对更多器件的控制越来越复杂,V3.0也引入了更多的Trigger功能,下图是简单的Trigger分类,本章节将一一做解释。

5.2 Standard Trigger

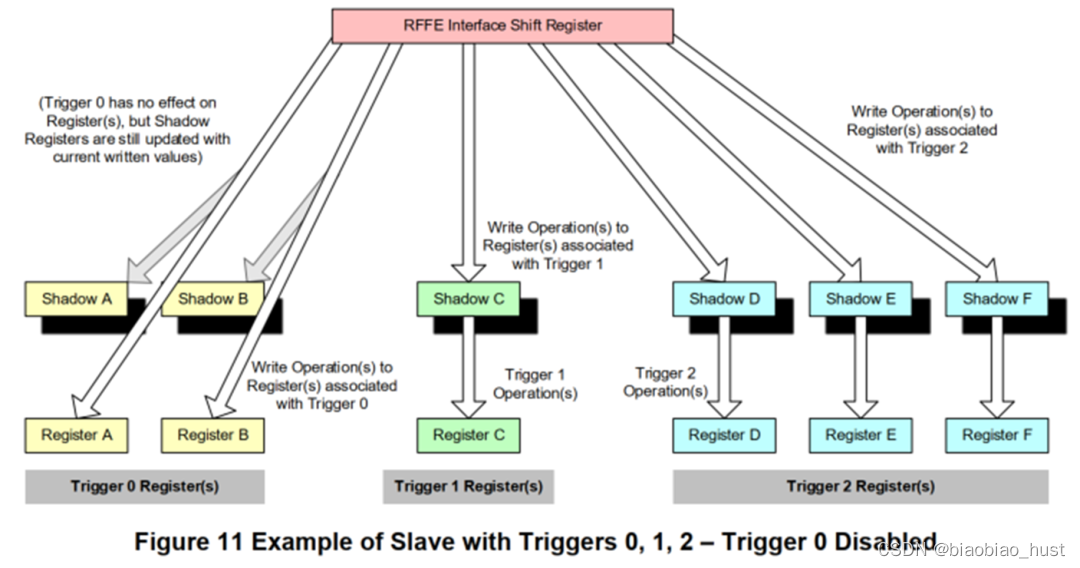

MIPI的Trigger机制如下图,为了支持Trigger模式,MIPI协议中引入了Shadow寄存器,用于存储未经触发的寄存器value:

-

当Trigger0 disable时,此时写入寄存器A/B的值直接生效,同时A/B寄存器对应的shadow register也同时更新为写入的值;

-

当Trigger1/2 enable时,此时寄存器C/D/E/F的写入值首先只能更新在对应的shadow register中,只有当Trigger1执行写入操作时,寄存器C才能正式生效,同理寄存器D/E/F也需要相同Trigger2操作。

-

每个寄存器只能对应1个或0个Trigger。

在实际操作中,MIPI RFFE中共有三个Standard Trigger,分别为Trigger0/1/2,受Reg0x1C[5:0]寄存器控制:

-

0x1C[5:3]:Trigger Mask,当Trigger Mask为0时,新写入值只更新到shadow register

-

0x1C[2:0]:Trigger Reg,当Trigger Mask为0,且Trigger Reg=1时,shadow register的value会转移到destination register

5.3 Extend Trigger

为了支持更多的寄存器Trigger数量,MIPI RFFE V2.1/3.0分别各引入了8个Trigger,工两组Block A和BlockB,统称为Extend Trigger。Extend Trigger的控制和Standard Trigger一样,对应的寄存器为0x2D~30。

需要注意的是,下文要讲的Timed Trigger和Mappable Trigger只能应用于Extend Trigger,不能用于Standard Trigger。

5.4 Timed Trigger

Timed Trigger顾名思义是在时间上对Trigger进行操作,具体就是提供寄存器在延时一定时间后生效,主要机制是对Trigger设置延时计数器生效。对应的延时计数器其实是由一个延时的计数寄存器进行控制。

Timed Trigger的工作机制如下:

-

当counter register的值=0,则此Extend Trigger属于正常Trigger

-

当counter register的值为非零时,寄存器的数则跟随时钟开始倒计时,直到值=0,Trigger生效

5.5 Mappable Trigger

如上介绍,我们了解到每个寄存器有且最多只能配置对应一个固定的Trigger,但随着5G的加入,射频前端越来越复杂,例如以下场景:

在5G手机中,可能有超过8路接收通路同时工作(CA场景),此时就需要同时控制8路LNA进行快速的AGC,每路LNA至少需要发送一个寄存器(~0.5us),然而5G的AGC切换是在symbol之间进行,而symbol与symbol之间只有一个CP的时间长度(当SCS=60kHz,时间为1.17us,如下图)来完成写入寄存器+LNA gain settle时间。因此要同时串行发送以上多路LNA是无法完成的。

Mappable Trigger提供这样一个可能,对寄存器不配置固定的Trigger,而是可编辑的Trigger,这样通过把所要控制的所有寄存器都配置到相同的Trigger,那么就可以在正式生效前做pre-setting,然后再同时Trigger。

Mappable Trigger具体操作如下:

- 定义一个寄存器叫mTrig set,4个bits对应一个BlockA/B Extend Trigger;

- 一个UDR寄存器最多只能配置一个mTrig set,或一个Fixed Trigger,不同同时配置两种Trigger;

- 当某个寄存器被配置为mTrig setA,且此时mTrig setA被写入成0b0010时,查表对应的Extend Trigger是ET05,则Extend Trigger05为当前寄存器及所有配置为mTrig setA的寄存器对应的Trigger;

- 当mTrig setA的值更新后,对应的Trigger也会同时更新;

- mTrig不会影响Timed Trigger,二者相互独立。