RISC-V与ARM

- RISC-V 架构

- RISC-V架构特点

- ARM 架构

- RISC-V 与 ARM

指令集架构 (ISA) 基本上是汇编级程序员,或编译器编写者可见的机器部分。 ISA 是软件与硬件相遇的地方。 ISA 定义了机器及其微架构本身可以理解的命令/指令,它还定义了如何存储、访问和实施指令。

我们使用计算机可以理解的语言向计算机的硬件发出指令。计算机语言由称为指令的词组成,词汇表称为指令集。指令集告诉我们每条指令的功能,以及指令在内存中的表达方式。

架构不会告诉您处理器是如何构建的。它告诉您处理器可以做什么。另一方面,微架构描述了处理器的构建和设计方式。微架构定义了缓存的数量和大小、指令周期数、流水线长度等。

了解了 ISA 是什么之后,我们现在继续概述 RISC-V 和 ARM 架构。

RISC-V 架构

RISC-V(发音为“risk-5”)是一种开放的 ISA,可供学术界和工业界免费使用。它构建并改进了原始的精简指令集 (RISC) 架构。

RISC-V架构特点

RISC-V 是一种读入-写出架构,意味着三件事:

- 它的算术指令只对寄存器进行操作,

- 只有加载和存储指令才能将数据写入和读出内存,

- 数据必须首先读入到一个寄存器,然后才能对其进行操作。

RISC-V 不会针对任何特定实现、微架构模式或部署目标进行过度架构/过度优化,因此它适用于所有计算目的。它能够做到这一点是因为它的 ISA 分为两部分,基本 ISA 和可选扩展。基本 ISA 被限制为,包含足以形成编译器目标,并满足现代操作系统的最小指令集。基础 ISA 不能重新定义,它存在于任何实现中。

根据实现要求,可以基本 ISA进行扩展。这允许 RISC-V支持广泛的定制和专业化。

内存系统使用小端字节序。小端字节顺序意味着多字节数据的最低有效字节存储在最低内存地址。

RISC-V ISA 包含一个名为 RVC 的压缩指令扩展,旨在通过用较短的 16 位指令编码替换常见指令,来减少静态和动态代码大小。同时也减少了每条指令的 CPU 周期数,但代价是增加了程序的指令数。它牺牲了代码密度来简化实现电路。

对于嵌入式系统,因为它们具有有限的指令存储容量。为了减少代码大小,RISC-V 使用其 RVC 扩展。 RVC 用较短的 16 位指令编码替换了常见的 32 位指令。

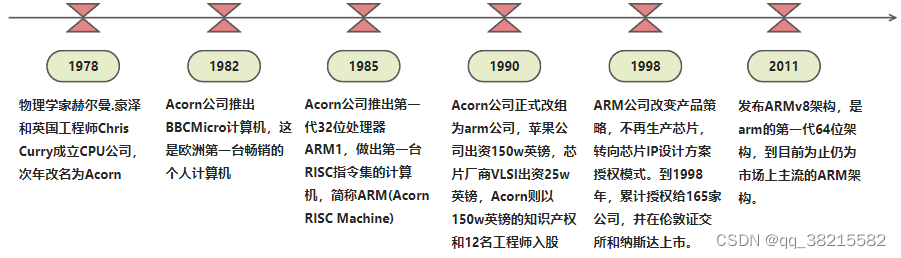

ARM 架构

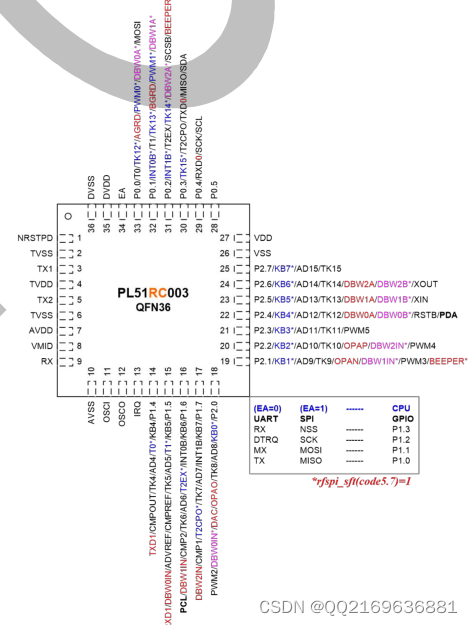

ARM是一种 RISC 架构。有 3 种不同类型的 ARM 架构用于不同的应用。它们是 A、R 和 M 架构。

- A-Profile(application profile):应用配置实现了传统的多模式ARM架构,支持基于MMU的虚拟内存系统架构。 这些配置支持 ARM 和 Thumb 指令集。优化以运行复杂的操作系统,如 Windows 和 Linux。它提供了最高的性能。

- R-Profile(real-time profile):实时配置实现了具有多种模式的传统 ARM 架构,并支持基于 MPU 的受保护内存系统架构。为安全关键环境提供高性能处理器,针对嵌入式控制系统等具有实时要求的系统,进行了优化。

- M-Profile(microcontroller profile):微控制器配置实现了一个为快速中断处理而设计的程序编写模型,具有寄存器的硬件堆栈,并支持用高级语言编写中断处理程序。 该处理器专为集成到 FPGA 中而设计,是极低功耗应用的理想选择。针对嵌入式系统,提供低延迟、高度确定性的操作。

| 架构 | 处理器位长度 | A系列 | M系列 | R系列 |

|---|---|---|---|---|

| ARMv6 | 32 | Cortex-M0 | ||

| ARMv7 | 32 | Cortex-A5, Cortex-A7, Cortex-A8, Cortex-A9, Cortex-A12, Cortex-A15, Cortex-A17 | Cortex-M3 | Cortex-R4, Cortex-R5, Cortex-R7, Cortex-R8 |

| ARMv7E | 32 | Cortex-M4 | ||

| ARMv8 | 32 | Cortex-A32 | Cortex-M23, Cortex-M33 | Cortex-R52 |

| ARMv8 | 64 | Cortex-A34 | Cortex-R82 |

ARM M系列CPU 的指令集很小,通常没有浮点单元,没有内存管理,没有缓存。 它们针对低成本,而非高性能进行了优化。 它们一般与 FLASH、RAM 和外围设备组合成一个微控制器芯片。 它们主要用于控制硬件,可以对裸机(没有库)进行编程,也可以与一些可以提供类似操作系统的功能的库链接。 这些 CPU 主要目的是代替其他各种8位和16位微控制器。

ARM A系列CPU 具有更大的指令集,并且它们通常包括浮点单元、内存管理单元和缓存。 它们针对高性能,而不是低成本进行了优化,对每单位功率的高性能进行了优化。 它们通常作为微处理器出售(通常与以太网、视频、mpeg 解码器等高端外围设备结合使用),需要另外提供片外 RAM 和闪存。 它们通常运行一些操作系统,通常是 Linux,操作系统提供核心地址空间和用户地址空间。这些CPU通常用于手机和平板电脑。

ARM架构的特点

它是一种具有 32 位寻址范围的加载存储架构。

与 RISC-V 不同,它不是开源 ISA,而是专有 ISA。

它对内存系统使用双端字节序。这意味着 arm 处理器/机器能够在硬件级别以两种字节序格式计算/传递数据。

它使用 Thumb 指令集来减少程序代码大小。

它是 32 位和 16 位长度指令集的混合体,对于具有内存大小和成本限制的系统(如嵌入式应用)具有最佳代码密度。它提供了 32 位指令集的高性能,几乎提供了 16 位指令集的代码密度。

RISC-V 与 ARM

现在我们对 ISA、RISC-V 和 ARM 有了深入的了解,我们将根据各种因素并排比较两者。

| 属性 | RISC-V 架构 | ARM 架构 |

|---|---|---|

| 专利 | 开源 | 专有 |

| RISC 架构 | ✓ | ✓ |

| 默认字节序 | Little-endian | Bi-endian |

| 支持 32 位和 64 位地址空间 | ✓ | ✓ |

| 代码压缩技术 | ✓ (RVC) | ✓ (Thumb) |

| 加载存储架构 | ✓ | ✓ |

| 分支延迟槽 | 无 | 无 |

- RISC-V 是开源的,而 ARM 不是。这意味着 RISC-V 是免许可和免版税的。

- RISC-V 允许用户免费使用新指令扩展 ISA,并创新 RISC-V 处理器的微架构,但 ARM 要求用户支付版税。这让RISC-V很快受到了很多厂商的欢迎。

- ARM被认为比RISC-V更复杂。另一个原因是,与笔记本电脑、台式机和服务器相比,ARM 对手机的优化过度。

- RISC-V 并未针对某一特定实现进行过度优化。它适用于所有计算系统,从微控制器到超级计算机。