Q:set_property bitstream.config.timer_cfg 这样的配置用于哪里?

A:https://www.cnblogs.com/lazypigwhy/p/10450406.html

FPGA通过CPU远程升级方案_bitstream.config.timer_cfg-CSDN博客

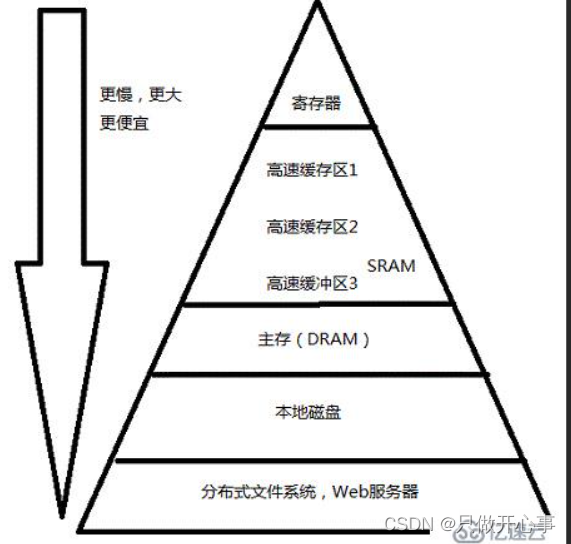

Q:逛论坛有人问,reg也可以实行sram的功能,且数据< 100bit的时候 ram的面积比reg实现的sram面积小,那在实现中如何选择?

A:我本来只是随便回复了一个,数据用ram,控制用reg,对方回我说他知道,他想问什么时候用reg去实现ram功能,什么时候用sram。于是我就去找了一些资料,在找资料的过程当中觉得现在的搜索引擎容易误人子弟(误,这是我的问题)。下面开始回答。

1)首先作为前端,我认为ram的实现方式是后端要关注的事情,在控制逻辑一样的情况下,选择面积较小的实现方式。(Area)

2)在同频率的情况下,bus对寄存器的读写是否可以做到流水?如果不能,那对于ram的访问速度比reg的访问速度要快很多吧。(Performance)

(3)sram作为静态存储,他的功耗,和reg的功耗不知道是怎么个对比,这个可能和sram从工艺上的实现方式有关。(power)

【在学的时候可能会觉得自己勤学苦练天道酬勤,但是可能后面发现自己当初钻牛角尖的问题有点傻逼。发问就像是,如果不考虑钱你最想要什么。】

Q:代码综合以后,资源没有or 不显示是什么原因,design是c910,

用quartus 综合,在hierarchy上可以看到模块,但是没有报资源。

用vivado综合,代码的hier上可以看到模块,但是utilization中找不到top1

A:可以查看编译报告里是否有相关警告,也可以看看RTL视图,这个模块相关的端口有没有显示没有连接或者接地。经过代码查看,pad_core_rst_b被接0;之前没有遇到过类似情况是因为一般拿到的代码都仿真过,c910不是自己公司出的design,风格不熟悉。仿真环境也没搞好,没有仿过。

下周待解决

1.zynq PL写DDR的笔记

2.c910 仿真环境调试