报错与错误

循环显示

停止时,不应该让读地址回到0

因为所谓队列为空,只是逻辑上为空,实际上并不是空,实际上依然存着之前存的数据

如果让读地址回到0,就会导致显示为不空,即读写地址不一致,然后再读一遍到写的地址,读完之后回到0,再读一遍的循环

结束时就是要让读地址和写地址重合,这样就没问题了

报错1

[DRC MDRV-1] Multiple Driver Nets: Net nolabel_line17/dual_port_RAM/UNCONN_OUT[1] has multiple drivers: nolabel_line17/dual_port_RAM/show_OBUF[6]_inst_i_2/O, and nolabel_line17/dual_port_RAM/rdata_reg[1]/Q.

关键词是multiple drivers。同一个变量,在不同的always 或者assign中被赋值,造成冲突。这在Verilog语言中是不被允许的。尤其是在复制一段代码之后,漏掉要修改的变量名,很容易导致这个问题。

原因就是data这个数据,在双端口RAM里赋值过一次了,但在显示的过程中,根据复位信号又赋值了一次,就会导致在多个文件里多次对同一个变量赋值,从而报这个错

解决方法就是去掉在显示部分里的赋值,只保留在RAM里的就行

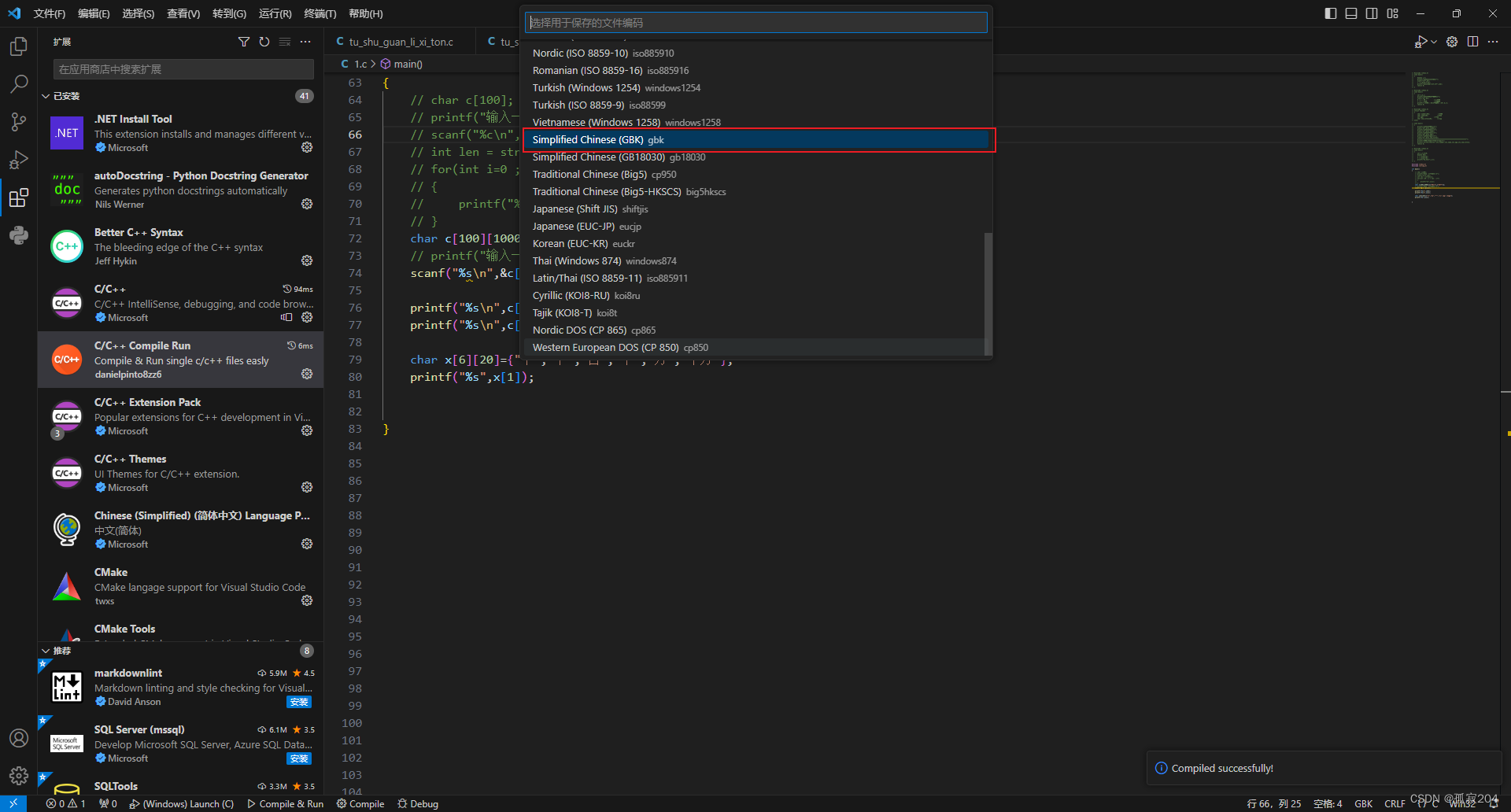

赋值规范:

“在描述组合逻辑的always块中使用阻塞赋值,则综合成组合逻辑的电路结构。”

“在描述时序逻辑的always块中使用时序赋值,则综合成时序逻辑的电路结构。”

阻塞与非阻塞赋值的使用原则:

原则1:时序电路建模时,用非阻塞赋值。

原则2:锁存器电路建模时,用非阻塞赋值。

原则3:用always块描述组合逻辑时,采用阻塞赋值。

原则4:在同一个块中描述时序逻辑和组合逻辑的混合逻辑时,用非阻塞赋值。

原则5:同一个always块中只能全用阻塞赋值或者全用非阻塞赋值。

原则6:不能在多个always块中对同一个变量进行赋值。