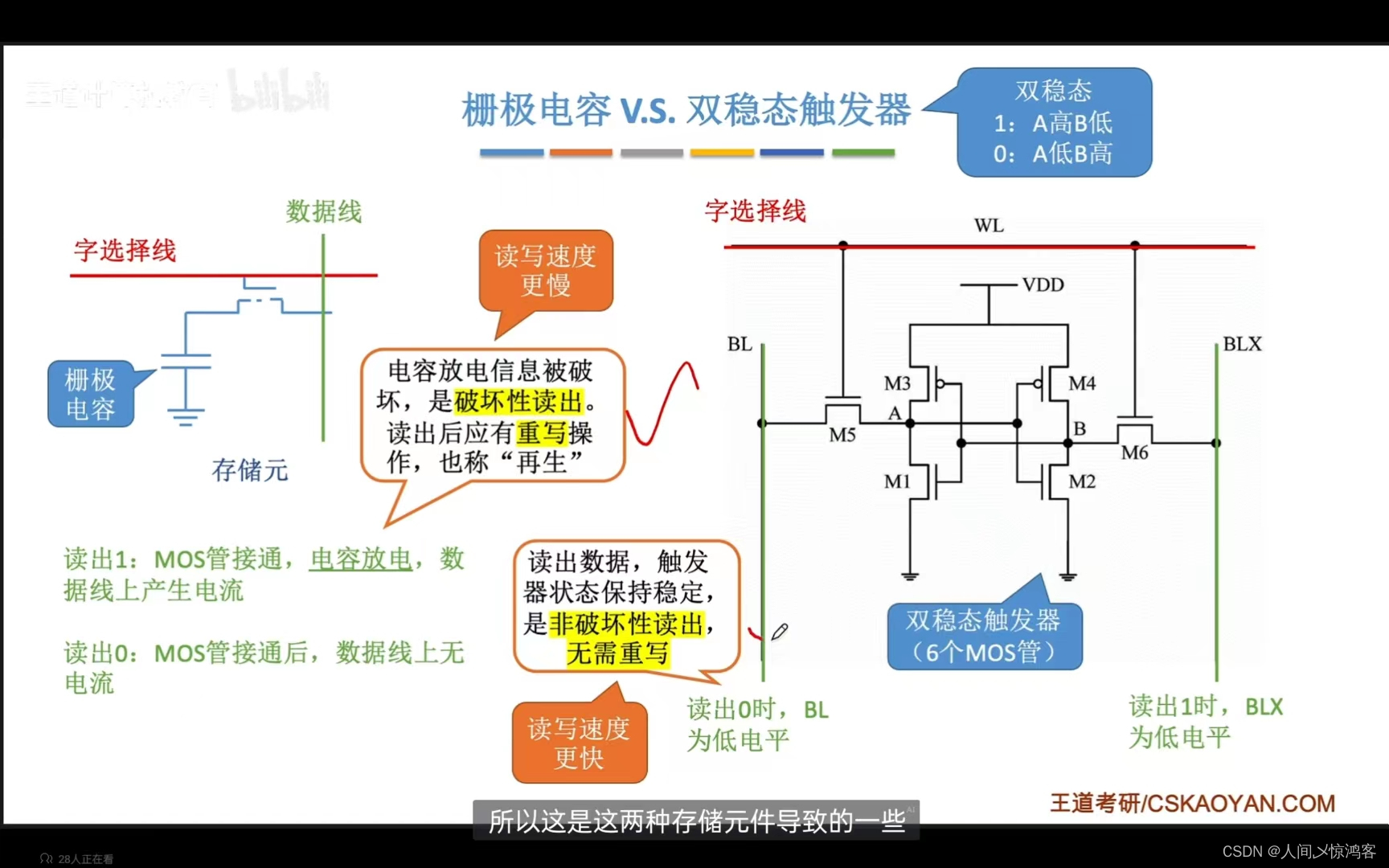

SRAM和DRAM:

DRAM:动态RAM(随机存期存储器),是使用栅极电容存储信息的;

SRAM:静态RAM,是使用双稳态触发器存储信息的。

重点在于DRAM由于要通过电容放电来表示信息,所以读出时是破坏性的(电容放电之后,电容上就没有电了,所以读出后要重新充电,也就是重写操作),而SRAM是通过触发器的状态(高电平或者低电平)来表示数据的,在读取的时候是非破坏性的,不需要重写,这也就造成了两者读写速度的不同。

DRAM的每个存储元制造成本低,集成度高,功耗低,且由于电容内的电荷只能维持2ms,即使不断电,2ms后信息也会消失,这就导致需要在2ms内必须刷新一次(也就是给电容充电)

而SRAM的每个存储元制造成本更高,集成度低,功耗大,由于SRAM是通过触发器电平的高低来表示数据的,所以只要不断电,数据就不会消失。

所以由于DRAM既要读后重写,又要不断刷新,所以访问延迟就比较高,但由于集成度高,存储密度大,所以往往被用作主存(RAM),以提供计算机程序所需的大量存储空间,相对的SRAM不需要刷新,可以立即访问,所以访问速度快,但集成度低,存储密度小,所以往往被用来作Cache。(高速缓冲存储器)

只读存储器ROM:

RAM芯片--易失性,断电后数据消失;

ROM芯片--非易失性,断电后数据不会丢失。

MROM -- 掩模式只读存储器

厂家按照客户需求,在芯片生产过程中直接写入信息,之后任何人不可重写(只能读出),可靠性高,灵活性差,生产周期长,只适合批量定制;

PROM -- 可编程只读存储器

用户可用专门的PROM写入器写入信息,写一次之后就不可更改;

EPROM -- 可擦除可编程只读存储器

允许用户写入信息,之后用某种方法擦除数据,可以进行多次重写;

UVPROM -- 用紫外线照射8~20分钟,擦除所有信息;

Flash Memory -- 闪速存储器(U盘,SD卡就是闪存)

每个存储元只需单个MOS管,位密度比RAM高,在EEPROM基础上发展而来,断电后也能保存信息,且可进行多次快速擦除重写。由于闪存需要线擦除再写入,因此闪存的写的速度要比读的速度更慢。

SSD -- 固态硬盘

由控制单元+存储单元(Flash芯片)构成,与闪速存储器的核心区别在于控制单元不一样,但存储介质都类似(存储介质都是闪存芯片),可进行多次快速擦除重写。SSD速度快,功耗低,价格高,目前个人电脑上常用SSD取代传统的机械硬盘。(手机辅存也使用Flash芯片,但相比SSD使用的芯片集成度更高,功耗更低,价格也更贵)

所以可以看出虽然ROM叫做只读存储器,但是很多ROM也是支持写的,且很多ROM也具有随机存取的特性。

计算机中的操作系统安装在辅存中,在开机的时候,主板上的BIOS芯片(ROM),存储了“自举装入程序”,负责引导装入操作系统。逻辑上,主存是由RAM和ROM组成的(实际上主板上的ROM芯(BIOS芯片)也是主存的一部分),且两者常统一编址。(比如主存中的ROM假如地址是 0~2047,那RAM就从2048开始编址)。

双口RAM,多模块存储器:

由于DRAM芯片的恢复时间比较长,有可能是存取时间的几倍,而CPU的读写速度比主存快很多,所以需要想办法提升主存速度。

双端口RAM;

双端口RAM的作用是优化多核CPU访问一根内存条的速度。

两个端口对同一个主存操作有可能出现问题的情况是两个端口对同同一地址单元进行操作时,

同时写入数据比较好理解,应该也不能说时写入错误,更像是后者写入会读前者写入的数据造成覆盖,同时对一个地址,一个写入,一个读出,写入其实应该没有什么问题,数据是存进去,但读出可能出现问题,因为原先数据可能已经被覆盖。

这个解决方法是:置 “ 忙 ” 信号为 0 ,由判断逻辑决定暂时关闭哪一个端口(即被延时),未被关闭的端口正常访问,被关闭的端口延长一个很短的时间段后再访问。

感觉机组由很多东西设计结构的不是很好描述,所以可能就放图比较多。

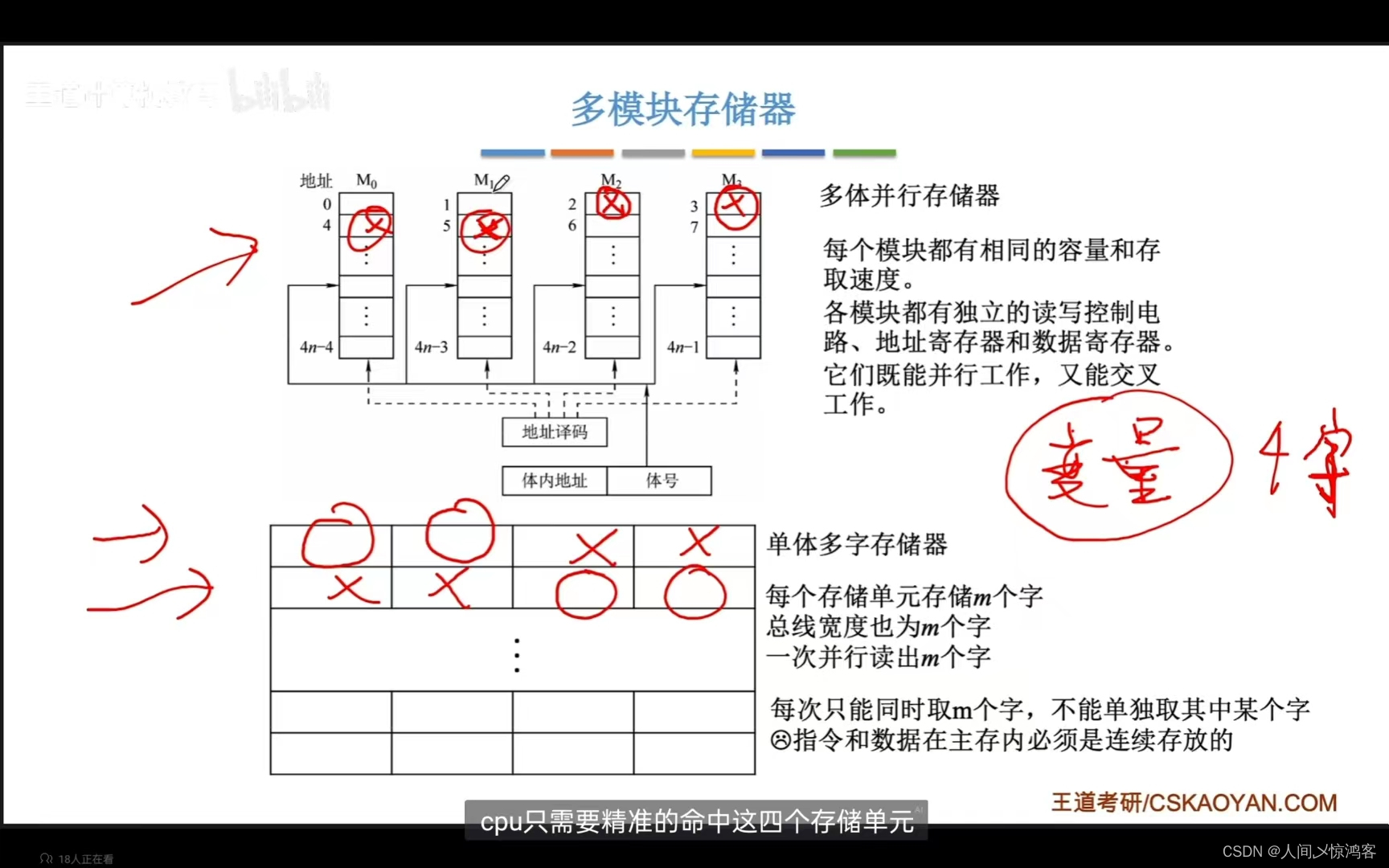

多体并存存储器:

高位交叉就是前面(高位)几位地址不一样,低位交叉就是后面几位地址不一样。

由于一次只能对主存访问一个数据(应该是存取的问题,上面提过主存是DRAM,读完之后要重写,需要时间恢复,而同于同一根内存条,如果未恢复,是无法开始下次读取的),所以对于高位交叉编址的存储器,如果连续访问的数据地址间隔不大,那么数据就大概率就存储再同一根内存条,这样只能等当前访问数据被重写之后才能进行下次访问,耗时可以从下图看出还是比较大的,但如果是低位交叉编址的话,这些数据就有可能存储在不同的内存条,那么如果在这根内存条读取之后,在这个内存条的恢复时期就可以开始在下一根内存条读取下一个数据,而当再次需要读取第一根内存条的时候,这根内存条可能已经结束重写的,这样就可以充分利用时间,甚至无缝衔接,从下图也可以看出低位交叉编址访问数据耗时远低于高位交叉编制。

宏观上,一个存储周期内,m体交叉存储器可以提供的数据量为单个模块的m倍。如果存取周期为T,存取时间为r,为了使流水线不间断,应保证模块数m>=T/r,如果前者小于后者,则需要CPU需要等待r,如果前者大于后者,则会导致前面的内存条闲置,相等的话则可以完美衔接。(有内存条闲置也不好,内存条也是要钱的,限制了这个内存条就有点浪费)(这里采用“流水线”的方式并行存取,宏观上并行,微观上串行,但我没有get到串并行的意思。)

这里根据所给地址来判断它属于第几个存储体的时候,可以用模余的方法,地址模上模块数,这个模余真的用处还蛮多的,可以留意一下。

多模块存储器通常是指将多个存储模块组合在一起,以提供更大的容量、更高的性能或更高的可用性。