目录

- 存储器

- 存储器分类

- 存储器常用性能指标

- 半导体存储器

- 随机存取存储器 RAM

- 动态随机存储器 DRAM

- 三态缓冲器

- 只读存储器 ROM

- 存储器与 CPU 链接

- 存储空间扩展方式

- 内存寻址方法(片选方式)

- 存储器小节思考题

- I/O 接口技术

- IO 接口概述

- IO 端口编址寻址

- 输入输出控制方式

- 并行通道与并行接口

- 串行通信与串行接口

- 同步通信与异步通信

存储器

存储器分类

按照材料分类:半导体存储器、磁性存储器、光盘存储器

只读存储器(readonlymemory, ROM):存储的内容固定不变,即只能读出不能写入

随机存取存储器(randomaccessmemory, RAM):既能读出又能写入的存储器称为随机存取存储器

按作用分类

- 主存储器:在主机内部,用来存放当前正在运行的程序和数据

- 辅助存储器:计算机外部设备

- 高速缓冲存储器 cache:很贵、高速、容量小

存储器常用性能指标

- 吞吐量(throughput):单位时间内处理的数据量,常用 MB/s 或 IOPS(每秒 IO 操作数)表示。

- 带宽(bandwidth):存储器能支持的最大数据传输速率,使用 bps(比特/秒)计量。

- 延迟(latency):数据访问的时间间隔,主要指读取或写入的数据要花多长时间。单位通常为毫秒(ms)。低延迟意味着性能更高。

- I/O Operations Per Second(IOPS):单位时间内执行的输入/输出(读/写)操作次数。

- 随机读写比例(random read/write ratio):存储器是否支持随机读写,随机读写性能如何。

- 可用容量(available capacity):存储器中实际可用的容量,需考虑格式化后、RAID 的副本数据等因素。

- 容量扩展性(scalability):存储器能够扩充到多大的容量。

- 磁盘存活时间(MTBF):平均故障间隔时间,衡量存储器的可靠性。

半导体存储器

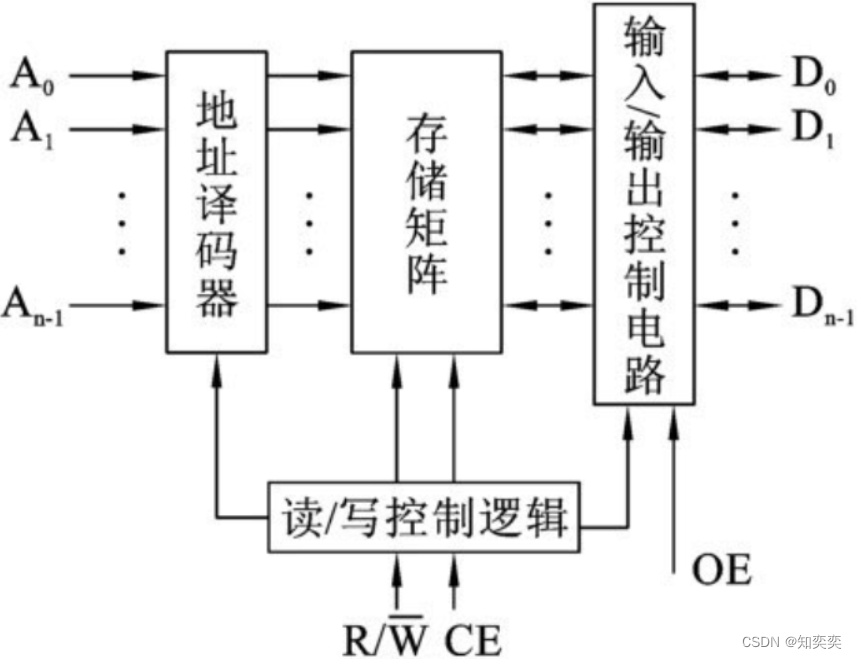

上图展示半导体存储器的体系结构

地址译码器:接收 CPU 发出的地址信号,然后产生地址译码信号,以便选中存储矩阵中的某个存储单元

存储矩阵:能够存储二进制信息的基本存储单元的集合

数据输入/输出控制电路:多为三态双向缓冲器结构,以便使系统中各存储器芯片的数据输入/输出端能方便地挂接到系统数据总线上

随机存取存储器 RAM

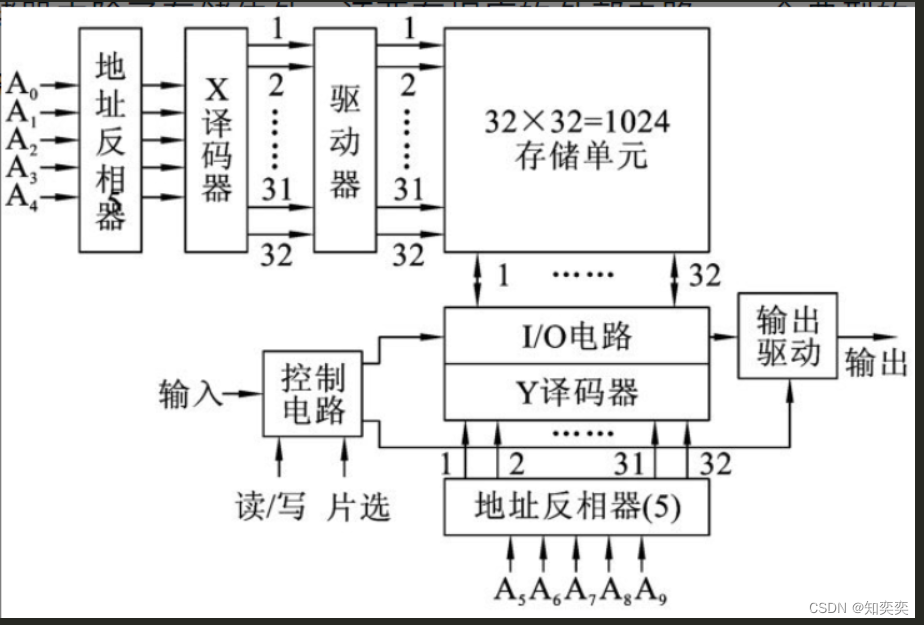

较大容量的存储器中,往往把各个字的同一位组织在一个片中;同一位的这些字通常排成矩阵的形式,如 32× 32=1024 或 64×64=4096。然后,由 X 选择线(行线)和 Y 选择线(列线)的重叠来选择所需要的单元

存储容量较小,也可以把 RAM 芯片的单元阵列直接排成所需要位数的形式

存储器的内部数据通过 I/O 电路以及输入和输出的三态门与数据总线相连

RAM 与 CPU 的连接,主要有以下三个部分

- 地址线连接

- 数据线链接

- 控制线链接

动态随机存储器 DRAM

行地址选通信号(Row Address Strobe,RAS)和列地址选通信号(Column Address Strobe,CAS) 对应的作用:

- RAS 信号控制行地址的写入,用来选择 DRAM 中的行。

- CAS 信号控制列地址的写入,用来选择 DRAM 中的列。

- 在行地址写入期间,列地址保持不变;在列地址写入期间,行地址保持不变。

- RAS 和 CAS 信号的时序关系严格,确定了 DRAM 的速度和性能。

- 一般情况下,必须先拉低 RAS 信号再拉低 CAS 信号。

据此,可以分析得到 DRAM 操作分为以下几个步骤:

- 向行地址线输入一行地址,拉低 RAS 信号进入行地址写入模式。

- 等待指定时序后,向列地址线输入一列地址,拉低 CAS 信号进入列地址写入模式。

- 等待指定时序后,根据读/写控制信号决定进行读操作还是写操作。

- 操作完成后,将 RAS 和 CAS 信号置高,退出当前操作模式。

地址锁存器(Address Latch)是计算机系统中一个很重要的组件。用于捕获和保存地址信息,以便后续处理,这是主要功能:

- 接收并存放地址信息。在地址锁存器中保存的地址可以来自 CPU 或者外围设备。

- 保持地址稳定。存储器访问通常包括地址阶段和数据阶段,这两个阶段存在间隔。地址锁存器可以在数据阶段保持地址信息不变。

- 提供后续模块使用。地址锁存器输出保存的地址,以供后续的计算或访问使用。

- 控制地址锁存时序。通过触发信号控制何时锁存地址,与后续模块协同工作。

通常情况下,地址锁存器用于存储器或外设的地址访问中。主要的工作过程为:

- 接收一个地址信息输入。

- 根据触发信号进行地址锁存,保存该地址。

- 输出锁存的地址,提供给后续模块使用。比如存储器或外围设备进行访问。

- 保持地址输出直到新的地址输入,实现数据访问的次数。

读周期 的具体步骤

- 地址阶段:CPU 输出内存地址

- 内存延迟:内存芯片检索数据

- 数据有效期:内存返回数据到数据总线上

- CPU 读取数据:CPU 从数据总线上获取数据

- CPU 使用数据:CPU 利用读取到的数据

三态缓冲器

三态缓冲器(Tri-State Buffer)是一种电路组件,主要用于控制数据总线上的信号。

三态缓冲器有三种可能的输出状态:

- 高电平:输出为逻辑 1。

- 低电平:输出为逻辑 0。

- 高阻态:输出三态(高阻抗),与数据总线脱离。

通过控制一个使能信号,三态缓冲器可以选择其输出状态。

主要特点为:

当使能信号有效时,三态缓冲器工作在正常工作模式(输出 0/1)。

当使能信号失效时,三态缓冲器进入高阻态,与数据总线脱离。

这时数据总线上的其它驱动器可以控制输出信号。

三态缓冲器的主要应用为:

共享数据总线。

中断数据流。

减少总线电流。

只读存储器 ROM

主要可将 ROM 分为以下几类

PROM(可编程只读存储器)

- 通过物理打洞编程,一次性编程。一旦编程后内容不可修改。

- 存储信息会在其中烧录,然后道具洞来锁定存储位

- 成本低、速度快、存储时间长

EPROM(光可擦可编只读存储器)

- 可以使用电子方法多次编程和擦除。

- 使用紫外光来擦除電路,然后使用编程器进行再编程

- 一次只能擦除整个 EPROM 芯片内容

EEPROM(电可擦可编只读存储器)

- 可以电子方式多次编程和擦除,不需要紫外光。

- 每个存储单元(字节)都可以单独编程和擦除。

- 成本高、速度较慢

FLASH ROM

- 类似于 EEPROM,但通过整个块来编程和擦除,速度比 EEPROM 快。

- 通过释放电子而擦除

- 每次最少可以擦除 64KB 的数据,最大可以整个芯片

- 成本介于 EPROM 和 EEPROM 之间

存储器与 CPU 链接

片选

通过高低电平选择对应芯片,一般存在一下两种电平选择方式:

高电平片选:当片选引脚拉高电平时,对应芯片被激活,可以工作。拉低电平则被禁止工作

低电平片选:反过来

片选的利用场景

- CPU 访问内存时通过地址译码器产生相应内存芯片的片选。

- 芯片组访问 PCI 设备时,需要为不同设备产生不同的片选信号。

- 组成多个内存通道时,为不同通道的内存产生不同的片选。

地址译码器

由于 cpu 发出的地址通常采用二进制编码,而存储器芯片内部通常采用一种独特的接线方式来标识地址。此时就需要该译码器来实现地址的转换

一般的,地址译码器有以下几种:门电路译码器、N 中取 1 译码器和 PLD (programmablelogicdevice,可编程逻辑器件)译码器

74LS138 是常用的 8 中取 1 译码器,输入 3 位二进制码,便在 8 个输出端产生一个低电平片选信号,因此也称为 3-8 译码器

存储空间扩展方式

位扩展、字扩展和字位扩展是计算机体系结构中的三种数据扩展方法。

位扩展是指通过在数据中添加额外的 0 位来扩展数据宽度。例如:

- 4 位数据

0011通过位扩展为 8 位为00110000 - 数据宽度从

n位扩展为n+m位,用m位 0 扩展。

字扩展是指通过使用相同的数据来组成多个相同的字来扩展字长。例如:

- 4 位

0011通过 2 倍字扩展为 8 位为00111100 - 数据宽度从

n位扩展为2*n位,重复相同的数据。

字位扩展是先进行字扩展,然后将高位与低位组合。例如:

- 4 位

0011先进行 2 倍字扩展得到00111100,然后将高低位组合为0011111100 - 数据宽度从

n扩展为2*n + n位。

这三种扩展方法的特点:

-

位扩展:添加 0,最简单但效率低。

-

字扩展:重复数据,常用于扩展少量数据。

-

字位扩展:充分利用数据,扩展效率高。

内存寻址方法(片选方式)

这是关于内存寻址方法常见的有三种:

线选法(Line Select):

- 通过激活相应的选线,实现对相应内存线的访问。

- 比如 8 条内存线,需要 3 条地址线 AAA,000~111 分别选择 0~7 号线。

- 简单实用但可寻址数量有限,只能访问 2^n 条线。

全译码法(Full Decode):

- 将地址完全译码,驱动相应的内存片选线。

- 比如 10 位地址需要 10 条片选线,可以访问 2^10=1024 个存储单元。

- 可寻址数量多但成本高,占用线路多。

部分译码法(Partial Decode):

- 将高地址 bit 部分译码,低地址 bit 采用线选法。

- 比如高 6 位译码驱动 64 条片选线,低 4 位通过线选选通其中一个。

- 可寻址 2^10 个单元,但只需 64 条片选线。

- 在可寻址数量和 complexity 之间找到平衡。

三种方法的比较:

- 线选法成本低但可寻址数量有限。

- 全译码法可寻址数量多但成本高,占用线路多。

- 部分译码法在可寻址数量和 complexity 之间取得平衡。

存储器小节思考题

为什么动态 RAM 需要定时刷新?

动态 RAM(DRAM)需要定期刷新是因为其存储单元采用一个电容器来保持电荷信息。

存储单元由一个闸管和一个电容器组成,电荷的有无表示存储的 0 和 1。但电容器会随时间慢慢泄漏电荷,信息将丢失。

为了防止电荷消失,DRAM 需要定期重新 charges 电容器,这个过程称为“刷新”或“刷新”。

CPU 寻址内存的能力最基本的因素取决于什么

地址总线、数据总线 位宽、总线(Front side bus)频率、指令集支持

I/O 接口技术

IO 接口概述

顾名思义,可得接口主要功能如下

(1)数据缓冲:实现高速 CPU 与慢速外部设备的速度匹配。

(2)信号转换:实现数字量与模拟量的转换、串行与并行格式的转换和电平转换

(3)中断控制:实现 CPU 与外部设备并行工作和故障自动处理等。

(4)定时计数:实现系统定时和外部事件计数及控制。

(5)DAM 传送:实现存储器与 I/O 设备之间直接交换信息。

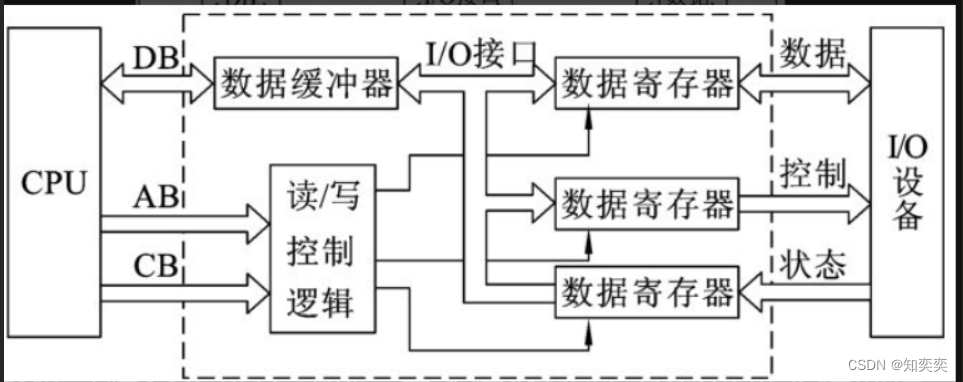

这是一个典型的 IO 接口电路结构图

数据寄存器是可读写的,用来存放 CPU 与 I/O 设备交换的信息。

控制寄存器用来存放 CPU 向外部设备发送的控制命令和工作方式设置等。

状态寄存器用来存放外部设备当前的工作状态信息,供 CPU 查询。

数据缓冲器是 CPU 与 I/O 设备信息传送的通道,它与 CPU 的数据总线 DB 连接,I/O 设备与 CPU 交换的信息都是通过数据缓冲器进行的。

IO 端口编址寻址

CPU 与外设通信时需要传输许多不同信息,将这些寄存器和它们的控制逻辑统称为 I/O 端口(port)

数据端口

存放外设送往 CPU 的数据以及 CPU 要输出到外设去的数据。这些数据是主机和外设之间交换的最基本的信息

状态端口

主要用来指示外设的当前状态。除了状态端口中的内容外,接口电路中往往还会有若干状态线,它们用电平的高低来指示外设当前的状态

命令端口(控制端口)

存放 CPU 向接口发出的各种命令和控制字,以便控制接口或设备的动作(常见的命令信息位有启动位、停止位、允许中断位)

I/O 端口的编址方式有两种,分别称为存储器映象寻址方式和 I/O 单独编址方式

存储器映象寻址方式

若把系统中的每一个 I/O 端口都看作一个存储单元,并与存储单元一样统一编址,这样访问存储器的所有指令均可用来访问 I/O 端口,不用设置专门的 I/O 指令

I/O单独编址方式

对系统中的 I/O 端口地址单独编址,构成一个 I/O 空间,它们不占用存储空间,而是用专门的 IN 指令和 OUT 指令来访问这种具有独立地址空间的端口

输入输出控制方式

这 4 种是程序设计与系统结构中常见的 I/O 控制方式:

程序控制方式(Program controlled I/O):

- 分为无条件传送和有条件传送两种方式

- 无条件传送:当外设已准备就绪,那就不必查询外设的状态而进行信息传输

- 有条件传送:CPU 通过执行程序不断读取并测试外部设备状态,如果输入外部设备处于已准备好状态或输出外部设备为空闲状态时,则 CPU 执行信息指令

中断控制方式(Interrupt controlled I/O):

- 当 I/O 完成时触发中断,跳转到中断服务程序。

- 使 CPU 在 I/O 就绪时进行处理,效率较高。

- 中断在程序间插入,需要保存超频信息等。有一定开销。

直接存取方式(Direct Memory Access,DMA):

当某一外部设备需要输入/输出一批数据时,向 DMA 控制器发出请求,DMA 控制器接收到这一请求后,向 CPU 发出总线请求。若 CPU 响应 DMA 的请求把总线使用权赋给 DMA 控制器,数据不通过 CPU,可直接由 DMA 控制器进行处理。当这批数据传送完毕后,DMA 控制器再向 CPU 发出“结束中断请求”,CPU 响应这一中断请求,即可收回总线使用权。

输入/输出处理机控制方式:

- 使用专用的 I/O 处理器负责与外围设备的交互。

- I/O 处理器独立于 CPU,专注于 I/O 操作。

- CPU 只需与 I/O 处理器通信,间接实现与外设的交互。

- I/O 处理器效率高,能有效减轻 CPU 压力。

四者效率:

程序控制方式 < 中断控制方式 < DMA < I/O 处理机

并行通道与并行接口

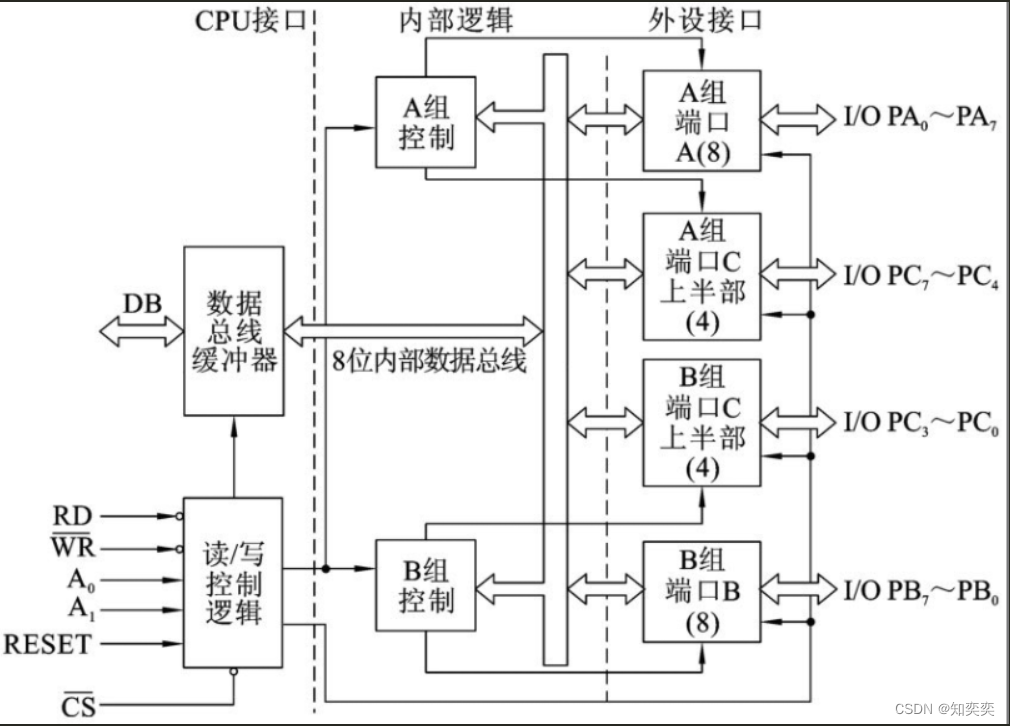

这是一个 8255A 结构的简单图

8255A 是一个可以提供 3 个 8 位通道的并行输入/输出接口芯片

通过编程其内部寄存器可配置每个端口为输入或输出模式。

主要通过控制字寄存器配置端口模式和方向,然后通过输入状态寄存器读取输入端口,或通过输出控制寄存器控制输出端口

串行通信与串行接口

调制解调器的作用是,进行数据的编码以及解码,使其更适合大数据的高速传输作用

信号的调制有以下三种

- 调频,使用频移键控法 FSK(frequencyshiftkeying)

- 调幅,使用幅移键控法 ASK (amplitude shiftkeying)

- 调相,使用相移键控法 PSK (phaseshiftkeying)

同步通信与异步通信

同步通信

指在约定的通信速率下,发送端和接收端的时钟信号频率和相位始终保持一致(同步)

- 发送端和接收端使用同一个时钟,基于该时钟进行同步工作,故传送数据的同时还要传送时钟信号

- 传输线路上始终保持连续的字符位流。若计算机没有数据传输,则线路上要用专用的“空闲”字符或同步字符填充。

- 发送端只会在时钟上升沿或下降沿发送数据,接收端也只在时钟相应沿接收数据

- 发送和接收之间没有手握信号,完全依赖时间,基于时钟周期来协调

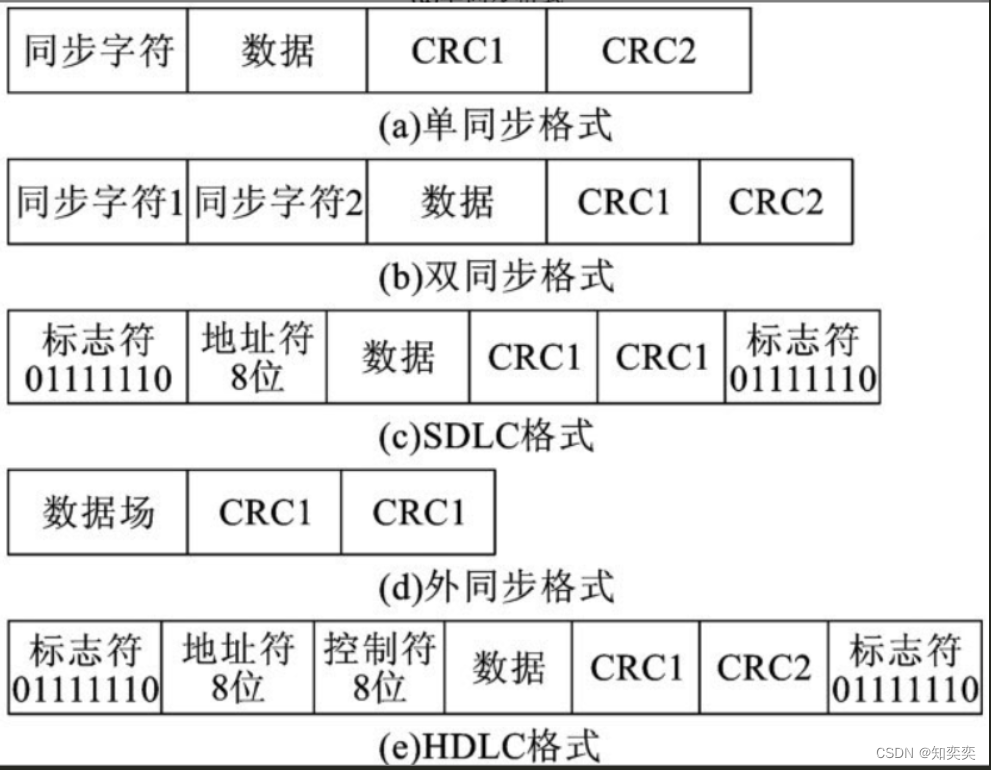

以下为几种常见的同步形式对应的数据段格式

异步通信

通信中两个字符之间的时间间隔是不固定的,而在一个字符内各位的时间间隔是固定的

- 规定字符由起始位(startbit)、数据位(databits)、奇偶校验位(parity)和停止位(stopbits)组成

- 传送一个字符时,由一位低电平的起始位开始,接着传送数据位;最后传送的是高电平的停止位;从停止位结束到下一个字符的起始位之间的空闲位要由高电平“1”来填充

- 发送端通过一个手动信号(如握手线)告知接收端数据有效,接收端基于该信号捕获数据

- 发送数据和接收数据间隔可以是任意时钟,完全不依赖时钟