1.实验目的和要求本实验为验证性实验,其目的是熟悉Qu artu s II 9.0 软件的使用,学会利用Qu artu s II 9.0 软件来完成整个EDA 开发的流程。

2.实验原理利用VHDL 完成电路设计后,必须借助EDA 工具中的综合器、适配器、时序仿真器和编程器等工具进行相应的处理后,才能使此项设计在 FPGA 上完成硬件实现,并得到硬件测试,从而使VHDL 设计得到最终的验证。Qu artu s II 是Altera 提供的FPGA/CPLD 开发集成环境,包括模块化的编译器,能满足各种特定设计的需要,同时也支持第三方的仿真工具。

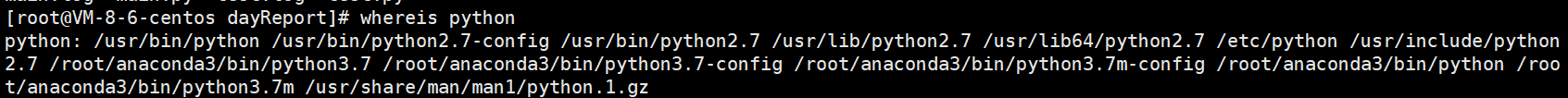

3.主要仪器设备(实验用的软硬件环境)实验的硬件环境是:微机一台GW48 EDA 实验开发系统一套电源线一根十芯 JTAG 口线一根USB 下载线一根USB 下载器一个实验的软件环境是:Quartus II 9.0 软件

4.操作方法与实验步骤利用Qu artu s II 9.0 软件实现 EDA 的基本设计流程:创建工程、编辑文本输入设计文件、编译前设置、全程编译、功能仿真。利用Qu artu s II 9.0 软件实现引脚锁定和编译文件下载。利用Qu artu s II 9.0 软件实现原理图输入设计文件的编辑和产生相应的原理图符号元件。5.实验内容及实验数据记录1)新 建工程(文本输入法)

6.实验数据处理与分析

1)任何一项设计都是一项工程(实验三中半加器、一位全加器以及8 位全加器的设计都应该新建工程,不可在同一个工程中进行设计) ,不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。

2)新建一个文件夹时应特别注意文件夹名不能用中文,最好也不要用数字。

2)编译工程结果将提示是否有错误或是警告,错误需要修改,警告则根据具体

情况进行修改。 (常见警告一个是未定义的引脚模式-改为输入高电阻模式,另一

个则是引脚未锁定,可在下载程序前再进行锁定)

3)时序仿真时候步骤:

A、File-〉new file->vector waveform file:新建波形文件

B、在波形文件下,右键单击选择 Insert node or bus..进行节点的添加

C、Assignments-〉Setting-〉Simulator Setting:选择功能仿真functional

D、电击仿真按钮进行仿真分析。

时序仿真时候注意点:

设置仿真时间区域。对于时序仿真来说,将仿真时间轴设置在一个合理的短

时间区域上十分重要。(由后续试验验证了此结论)通常设置的时间范围在

数十微妙之间:选择Edit->End Time

文件后缀名:.vwf

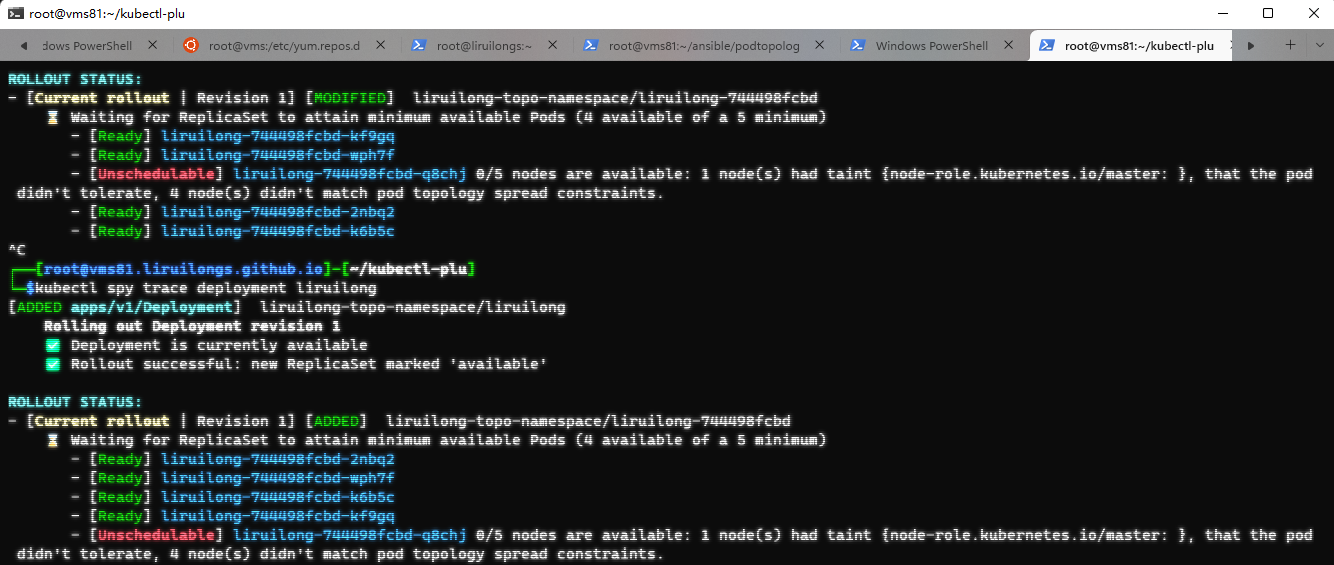

4)下载程序前应连接好下载线,开启电源,确保连线可用(我的电脑-)管理-〉

设备管理器-〉串行通信端口) ;其次在打开窗口中单击 Hardware Setup,选择

对应项;最后单击 START 进行下载,右上角有相关的下载进度提示,当提示为

100%时候表示下载成功。

7.质疑、建议、问题讨论

通过本次实验,对 Quartus II 9.0 软件有了初步的认识,在实验的基础上基本掌握了利用 Quartus II 9.0 软件实现EDA 的基本设计流程:创建工程、编辑 文本输 入 设计文件、编译 前设置、全 程编译 、功能仿真等 。