目录

一、前言

二、FSM_ENCODING

2.1 属性介绍

2.2 工程代码

2.3 结果

2.4 参考资料

一、前言

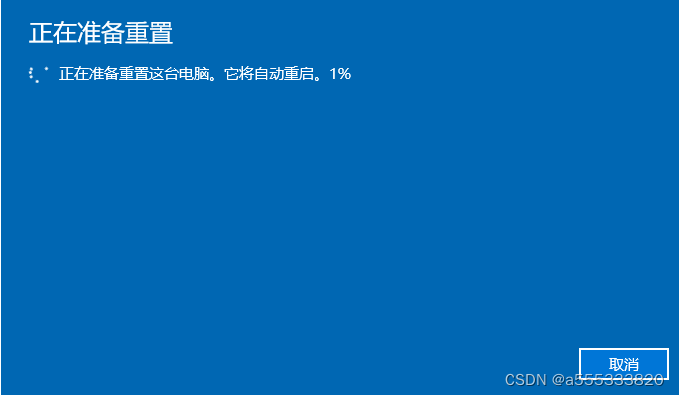

状态机的实现有很多方式,如auto,one_hot,sequential,如下图中Synthesis中-fsm_extraction的配置项,但此处作用范围为全局,如果要对部分状态机指定实现方式,则可通过在RTL代码中设置FSM_ENCODING属性。

二、FSM_ENCODING

2.1 属性介绍

FSM_ENCODING可以控制状态机的编码方式,属性放置于状态寄存器的前面,可设置的值有one_hot,sequential,johnson,gray,user_encoding,none,auto,默认值为auto,设置为auto时由综合工具决定编码方式,user_encoding则表示让综合工具综合出状态机,但是使用RTL中由用户设定的编码方式。FSM_ENCODING可以使用在RTL和XDC中。

使用格式:(*fsm_encoding="one_hot"*) reg state_machine;

2.2 工程代码

此处以一个常用例子序列1101检测的代码为例,检测到输入序列为1101则输出1,否则输出0,

module FSM( d,clk,rst,out);

input d,clk,rst;

output reg out;

(*fsm_encoding="sequential"*)reg [2:0] current_state,next_state;

parameter [2:0] s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100;

always@(posedge clk,posedge rst)

begin if(rst==1)current_state<=s0;elsecurrent_state<=next_state;

end

always@(*)

begin case(current_state)s0:if(d==1)next_state<=s1;elsenext_state<=s0;s1:if(d==1)next_state<=s2;elsenext_state<=s0;s2:if(d==0)next_state<=s3;elsenext_state<=s2; s3:if(d==1)next_state<=s4;elsenext_state<=s0;s4:if(d==1)next_state<=s2;elsenext_state<=s0; default:next_state<=s0;endcase

end

always@(*)

beginif(current_state==s4)out=1;elseout=0;

end

endmodule 2.3 结果

设置为gray时,综合结果如下图,网表名称自动加上gray

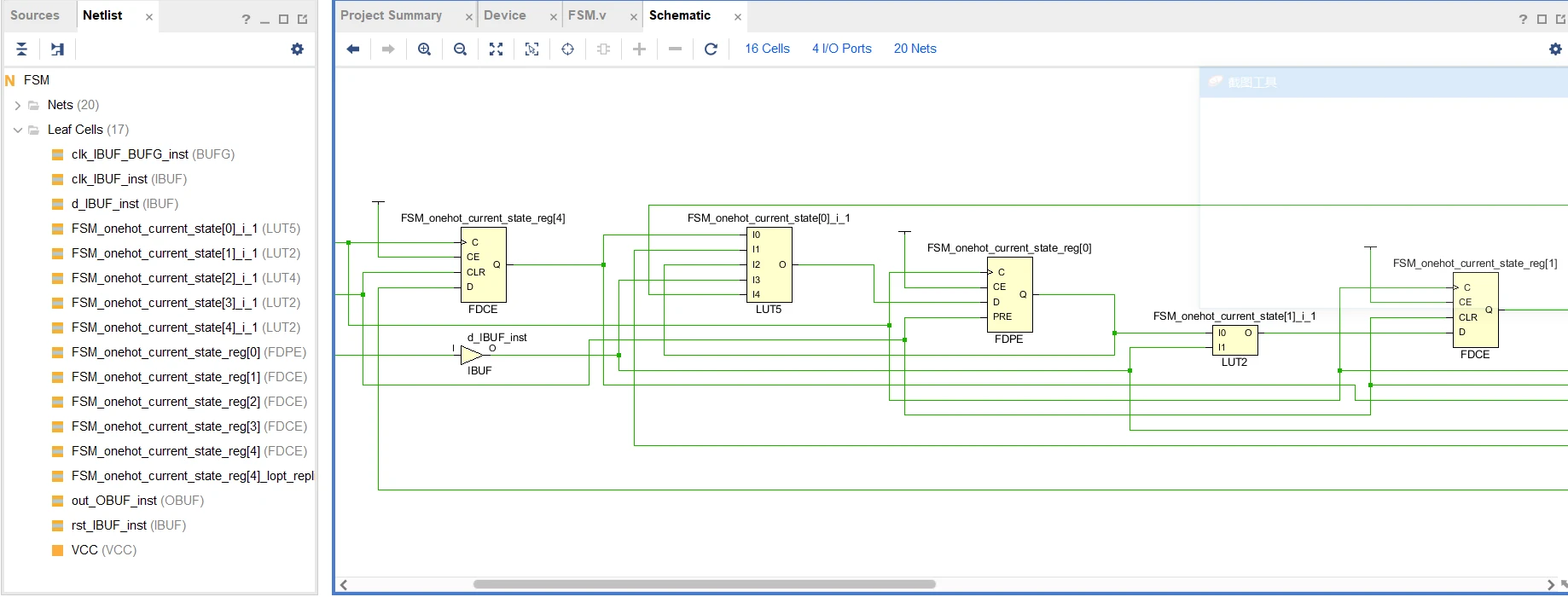

设置为one_hot时,综合结果如下图,网表名称自动加上onehot

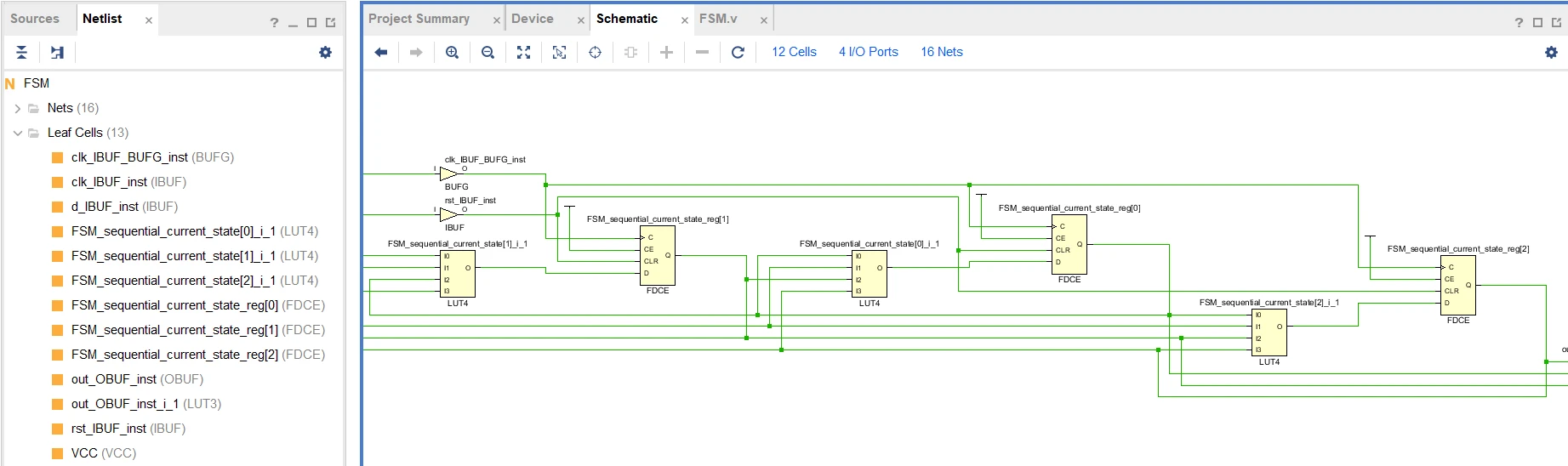

设置为sequential时,综合结果如下图,网表名称自动加上sequential,不同编码方式使用的LUT和FF资源类型和数量存在差异。

2.4 参考资料

用户手册《ug901-vivado-synthesis.pdf》

书籍《数字电路与FPGA设计》