时钟缓冲区类型

默认情况下,Vivado synthesis推断输入缓冲区和全局时钟缓冲区(IBUF/BUFG)

时钟端口的组合。但是,您可以使用IO_BUFFER_TYPE和

CLOCK_BUFFER_TYPE属性组合在一起,以指导Vivado合成工具更改

默认缓冲区类型,如IBUF/BUFR对,或没有带BUFIO时钟的输入缓冲区

缓冲器或者完全消除缓冲器。

强制逻辑优化(MLO),发生在link_design和

opt_design支持使用CLOCK_BUFFER_TYPE属性插入全局时钟

缓冲区。支持的值是7系列的BUFG,UltraScale的BUFG和BUFGCE,

UltraScale+和Versal设备。值NONE可用于所有体系结构

通过MLO和opt_ design抑制全局时钟缓冲器插入。对于BUFG值

opt_design和MLO插入相应的缓冲区类型来驱动

指定净值。

CLOCK_BUFFER_TYPE属性指示要推断的时钟缓冲区类型

指定的网络或端口对象。IO_BUFFER_TYPE属性指示是否推断

端口的输入或输出缓冲区。

提示:CLOCK_BUFFER_TYPE属性的使用意味着在目标网络上有一个KEEP,它保留

网络名称,并防止通过RTL优化移除网络。

CLOCK_BUFFER_TYPE可以在RTL或XDC中定义。当在RTL中指定时

属性可以附加到端口。合成后,属性CLOCK_BUFFER_TYPE应为

连接到由输入缓冲器驱动的网络。

注意:MAX_FANOUT不适用于具有CLOCK_BUFFER_TYPE的网络

应用对象:

•端口(get_Ports):将CLOCK_BUFFER_TYPE应用于任何顶级时钟端口,以描述类型

使用或不使用时钟缓冲器。对于7系列、UltraScale和Ultra-Scale Plus

属性只能在RTL内部的端口上设置,在端口上设置时opt_design不会使用

通过XDC。对于Versal,opt_design仅支持通过XDC的端口上的CLOCK_BUFFER_TYPE

用于OOC实现。对于任何其他流,应该在由

顶级端口。

•网络(get_Nets):将CLOCK_BUFFER_TYPE应用于连接到顶级的任何信号

时钟端口(合成)或任何网络(逻辑优化)来描述什么类型的时钟缓冲器

使用或不使用时钟缓冲器。

价值观

•BUFFCE、BUFG、BUFH、BUFIO、BUFMR、BUFR:指示工具推断指定的时钟

用于时钟端口或网络的缓冲器。

•无:指示工具不推断时钟的任何时钟缓冲区。

注:与IO_BUFFER_TYPE“NONE”一起使用可防止Vivado合成推断出任何缓冲区。

vivado CLOCK_BUFFER_TYPE

embedded/2024/10/22 16:38:42/

Syntax

Verilog Syntax

(* clock_buffer_type = "none" *) input clk1;

VHDL Syntax

entity test is port(

in1 : std_logic_vector (8 downto 0);

clk : std_logic;

out1 : std_logic_vector(8 downto 0));

attribute clock_buffer_type : string;

attribute clock_buffer_type of clk: signal is "BUFR";

end test;

XDC Syntax

set_property CLOCK_BUFFER_TYPE BUFMR [get_nets <net_name> ]

相关文章

顺序表与链表学习笔记

顺序表及其结构定义

(1)结构定义

顺序存储: 顺序表的元素按顺序存储在一块连续的内存区域中,每个元素占用相同大小的存储空间。通过数组实现,每个元素可以通过下标快速访问。 存储密度高: 因为顺序表使用…

Spring:Spring中分布式事务解决方案

一、前言 在Spring中,分布式事务是指涉及多个数据库或系统的事务处理,其中事务的参与者、支持事务的服务器、资源管理器以及事务管理器位于分布式系统的不同节点上。这样的架构使得两个或多个网络计算机上的数据能够被访问并更新,同时将这些操…

Pegasus平台Pytorch源码编译

和Drive PX2的编译没有什么区别

源码编译步骤

注意:当完全按照以下步骤进行编译时,如果出现错误,注意检查CUDA版本、对应的库是否存在

# Download PyTorch sources

git clone --recursive --branch <version> http://github.com/pyt…

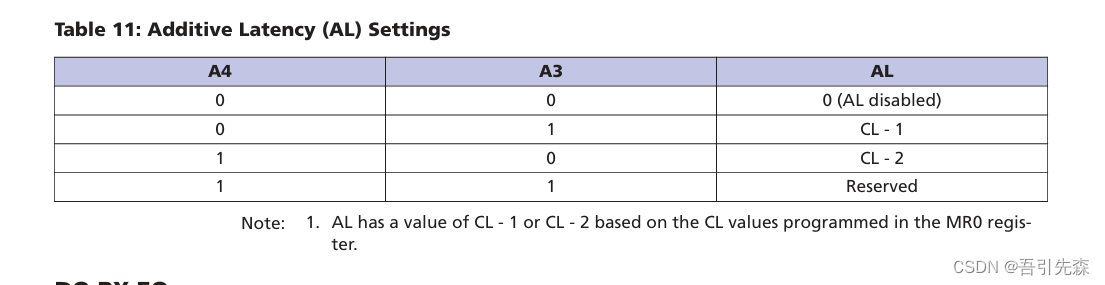

关于FPGA对 DDR4 (MT40A256M16)的读写控制 4

关于FPGA对 DDR4 (MT40A256M16)的读写控制 4 语言 :Verilg HDL 、VHDL EDA工具:ISE、Vivado、Quartus II 关于FPGA对 DDR4 (MT40A256M16)的读写控制 4一、引言二、DDR4 SDRAM设备中模式寄存器重要的模式寄存…

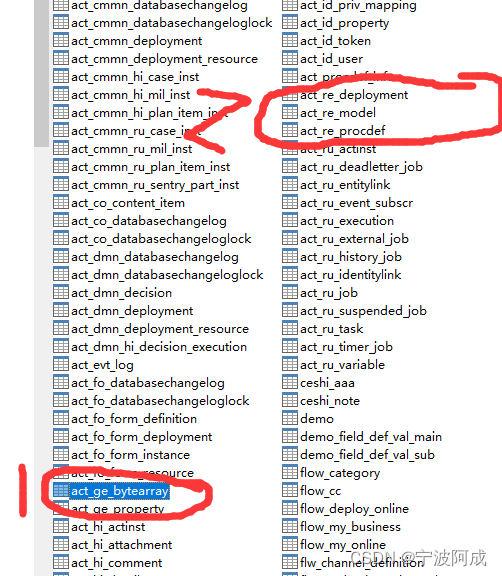

清空flowable的表定义的相关表

更多ruoyi-nbcio功能请看演示系统

gitee源代码地址

前后端代码: https://gitee.com/nbacheng/ruoyi-nbcio

演示地址:RuoYi-Nbcio后台管理系统 http://218.75.87.38:9666/

更多nbcio-boot功能请看演示系统

gitee源代码地址

后端代码: h…

[渗透测试] 任意文件读取漏洞

任意文件读取漏洞

概述

漏洞成因

存在读取文件的功能(Web应用开放了文件读取功能)读取文件的路径客户端可控(完全控制或者影响文件路径)没有对文件路径进行校验或者校验不严格导致被绕过输出文件内容

漏洞危害

下载服务器中的…

深度剖析:前端如何驾驭海量数据,实现流畅渲染的多种途径

文章目录 一、分批渲染1、setTimeout定时器分批渲染2、使用requestAnimationFrame()改进渲染2.1、什么是requestAnimationFrame2.2、为什么使用requestAnimationFrame而不是setTimeout或setInterval2.3、requestAnimationFrame的优势和适用场景 二、滚动触底加载数据三、Elemen…

嵌入式存储新选择:STM32与W25Q64 Flash的高效SPI集成

摘要

在嵌入式系统设计中,选择合适的存储设备对于确保系统性能和可靠性至关重要。W25Q64 Flash存储器以其高容量、低功耗和高擦写次数成为理想的选择。本文将介绍如何将W25Q64 Flash存储器与STM32微控制器通过SPI接口高效集成,包括硬件连接、SPI配置和实…

![[渗透测试] 任意文件读取漏洞](https://img-blog.csdnimg.cn/direct/440dc721b9004c80b6b3d3fade0ce0ad.png#pic_center)