系列文章目录

文章目录

- 系列文章目录

- 前言

- 一、亚稳态是什么

- 二、亚稳态概率

前言

马上成为新ICer,利用空闲时间展开对自己的首轮培训,取名为”新芯计划“哈哈哈

这个系列主要给自己做个基础知识的巩固,本节的内容围绕亚稳态展开,如若有内容有误,欢迎和感谢各位指正

参考文章:MTBF 是如何指导跨时钟域设计的

一、亚稳态是什么

亚稳态发生于 :

- 输入数据不满足时钟的建立/保持时间

- 复位信号不满足时钟的Recovery/Removal时间

以不满足建立时间为例:

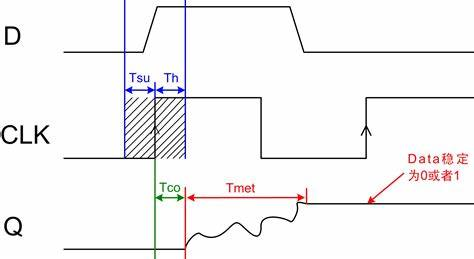

经过寄存器延时 T c o T_{co} Tco,经过 T m e t T_{met} Tmet的振荡时间,此时间段内信号不稳定,在0和1之间变化,即为亚稳态,当振荡结束回到稳定状态0或者1,这是随机的。亚稳态往后传播可能导致系统电路瘫痪,影响恶劣,因此跨时钟的同步设计是非常重要的一环,跨时钟域所做的一切努力,只是为了防止亚稳态造成电路功能失败。

二、亚稳态概率

亚稳态发生概率通常使用MTBF(Mean Time Between Failure)值来衡量:

M T B F = e t M E T / T a u T o ∗ f C L K ∗ f D A T A MTBF = \frac{e^{t_{MET}/T_{au}}}{T_{o}*f_{CLK}*f_{DATA}} MTBF=To∗fCLK∗fDATAetMET/Tau

MTBF表示亚稳态导致电路功能失败的平均时间,其值越大,表示失败发生所需要的时间越长,那么电路就越稳定

式中,

- T a u T_{au} Tau和 T o T_{o} To为常数,由芯片制造工艺和工作环境决定

- t M E T t_{MET} tMET为等待亚稳态稳定的可用时间,其值越大表示亚稳态在此时间内越可能恢复到稳定状态,电路越可靠

- f C L K f_{CLK} fCLK表示接收时钟域的时钟频率

- f D A T A f_{DATA} fDATA表示待接收信号所在时钟域的时钟频率

MTBF 影响了哪些跨时钟域的设计细节 ?

参考文章:MTBF 是如何指导跨时钟域设计的

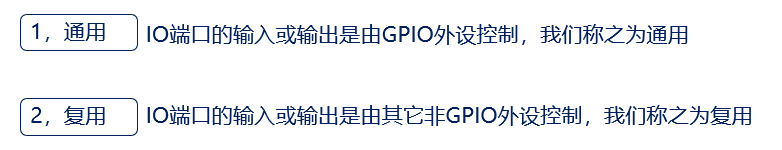

- 源时钟域异步信号要寄存器输出

寄存器输出可以避免毛刺,毛刺意味着什么,异步信号的跳变。也就是说寄存器输出可以减少异步信号的跳变,即减小 fdata 的值,使 MTBF 变大,电路则更不容易失败。

- 时钟频率越高时,同步器级联的寄存器数目越多

时钟频率越高,fclk 越大,MTBF 越小,电路越容易因为亚稳态失效。因此为了增大 MTBF 的值,可以通过增加级联的寄存器,从而增加 tMET 的值

- 布局约束时,同步器级联的寄存器越近越好,尤其是当时钟频率很高时

当 FF1 与 FF2 越近,FF1 与 FF2 的连线越可能短,FF2 的 timing slack 则越大,tMET 的值便越大,因而 MTBF 越大。

同步化不仅要考虑打拍级数(一般>300MHz,打拍级数>5),还要考虑后端约束:

Xilinx 有两个专门的约束:

1. ASYNC_REG="TRUE" :约束同步寄存器尽可能靠近2. SHREG_EXTRACT="NO" :约束同步寄存器不被综合成移位寄存器