FPGA在进行相关算法计算时,一般都会使用高级语言进行算法验证,目前比较常见的就是 MATLAB ,那么使用哪种方式可以将MATLAB中实现的算哒转换到FPGA中?

目前可以通过多种方式在 FPGA 中实现算法。

Simulink HDL Coder

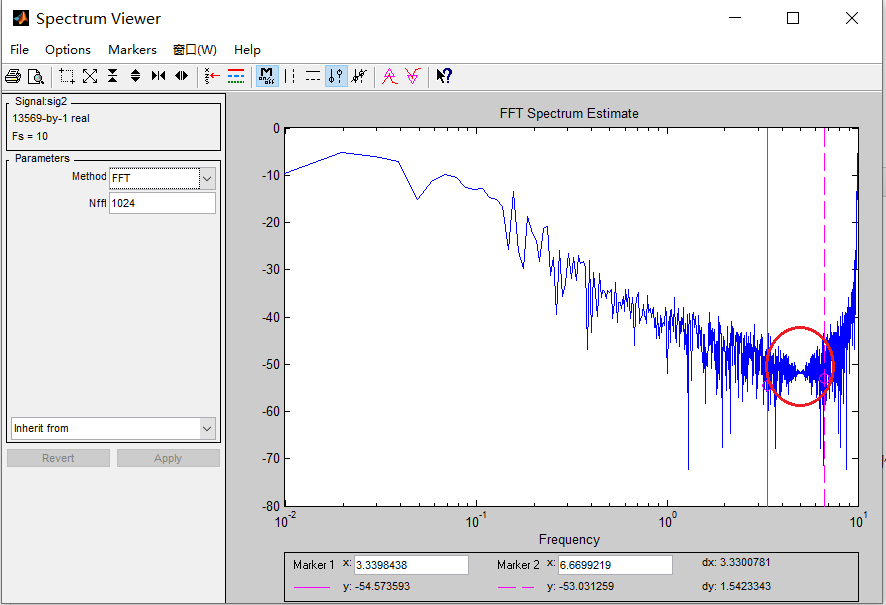

MathWorks 提供了一个名为 Simulink HDL 编码器从 Simulink 模型和嵌入式 M 代码创建可综合的 HDL。Simulink HDL Coder对于快速评估硬件中的新算法非常有用。但是,使用 Xilinx System Generator 工具可以实现更高的性能。

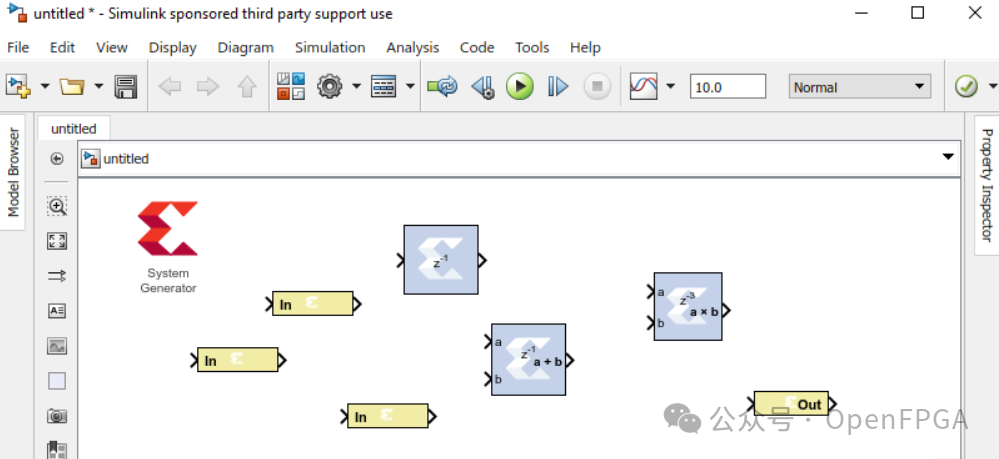

System Generator for DSP

Xilinx System Generator for DSP:Xilinx 提供了一个高度优化的模块库,可以在 Simulink 中进行仿真,然后编译用于 FPGA 上运行。设计时候需要使用 MATLAB Simulink 环境中,并用 System Generator 模块替换 Simulink 的模块。此设计流程提供比 HDL Coder 更高的性能,因为每个模块都是针对 Xilinx FPGA 预先优化的 IP。

Synphony HSL

Synopsys(Synopsys, Inc. (NASDAQ: SNPS) 是全球领先的半导体设计、验证和制造软件和 IP 供应商) 有一个高级综合工具 (HSL),称为 Synphony HLS。

Synphony HLS 解决方案具有以下优势,可显著提高生产率,优于传统方法:

从 M 到优化 RTL 的自动化流程

ASIC 和 FPGA 优化 RTL 架构的综合

用于早期算法验证的快速原型方法

与低效且容易出错的手动重新编码流程不同,Synphony HLS 直接从高级 M 代码和 Synphony HLS 优化的 IP 模型库创建可实施的 RTL 和 C 模型。使用独特的约束驱动定点传播功能,设计人员可以快速直观地从可综合的高级浮点 M 代码子集中导出定点模型。然后,Synphony HLS 引擎将合成经过架构优化的 RTL,满足面积、速度和功率目标。

我还没有使用过这个工具,所以不能评论他们的设计流程。这听起来类似于Xilinx停产的工具-AccelDSP,这为快速原型化MATLAB算法和目标FPGA硬件提供了一种很好的方法。然而,它通常不会产生高性能的设计。

手动HDL编码

最后一个选项是手动编码。理解算法做了哪些运算,尝试从硬件角度理解。 通常所有的算法都可以在硬件中通过乘法、加法、减法、除法等基本运算来实现。为此,需要verilog编程技能和数字设计等方面知识。根据MATLAB算法,从头开始,使用VHDL或Verilog(可能实例化Xilinx IP)编写设计代码,创建HDL测试平台,并将MATLAB的输入/输出向量与HDL仿真器进行比较。几十年来,工程师们一直以这种方式进行设计,但这是一种缓慢且容易出错的方式。与 MathWorks HDL Coder 一样,它确实具有产生不依赖于特定软件工具的 HDL 设计的优势,同时兼具占用资源少等优点,然而也就这些优点而已。

总结

从方便快捷出发,优选System Generator for DSP,但是无法说服每一个人,所以还是手动编写吧~