文章目录

DSP-toc" style="margin-left:40px;">TI DSP

C2000-toc" style="margin-left:40px;">C2000系列

TMS320F28003X

典型应用

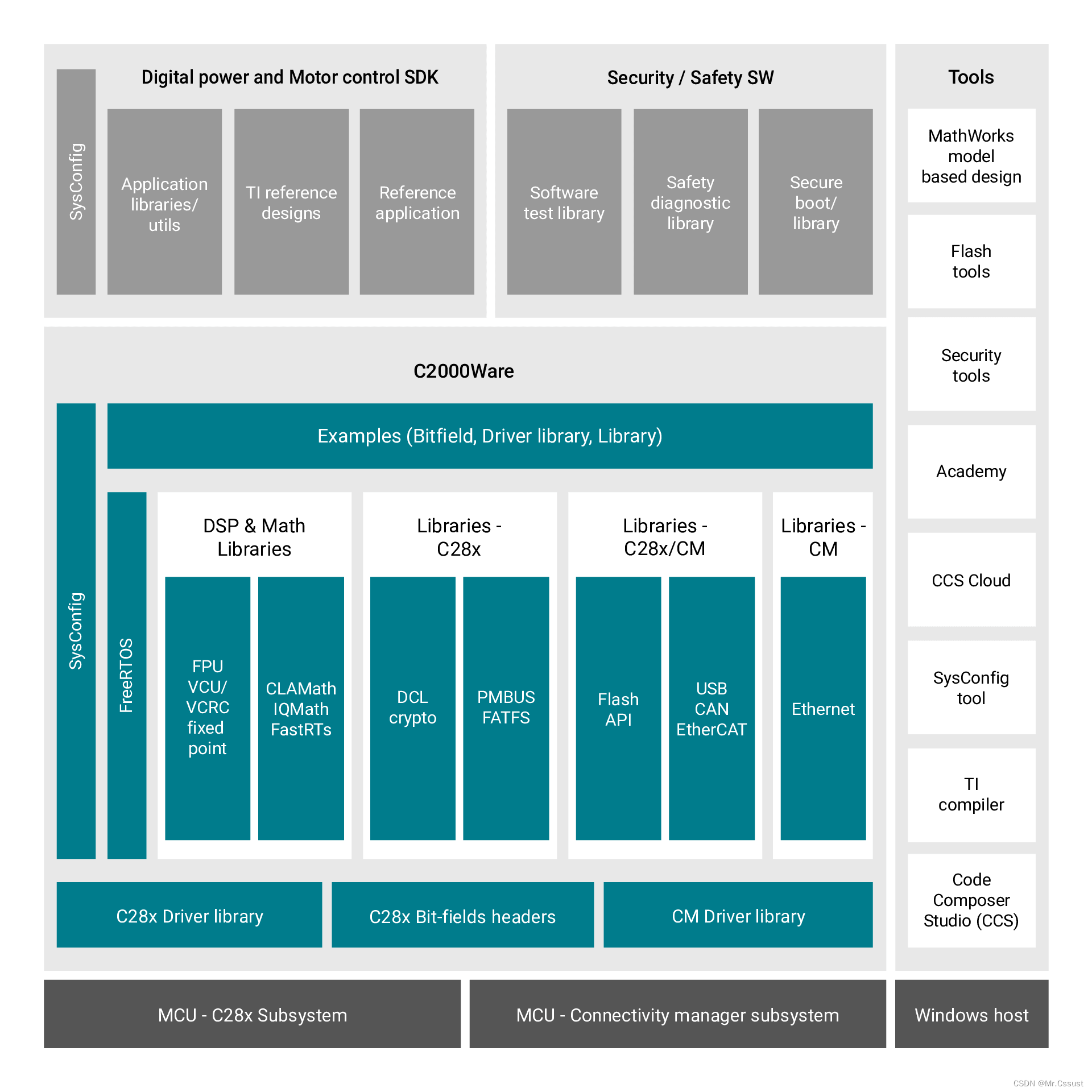

开发工具链

参考资料

DSP" style="margin-left:0;text-align:justify;">TI DSP

TI C2000系列 控制领域

TI C5000系列 通信领域

TI C6000系列 图像领域

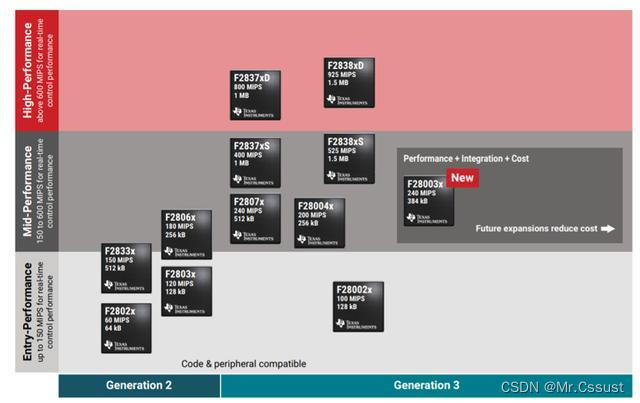

C2000" style="margin-left:0;text-align:justify;">C2000系列

第三代集成了C28浮点DSP内核,采用了65nm工艺(上一代180nm)

第四代正在规划中,将内置C29 DSP内核,性能提高2至3倍

TMS320F28003X

C2000F28003X包括一个120MHz主频的32位C28 浮点DSP,以及一个120MHz主频的CLA。CLA (Control Law Accelerator,控制率加速器)独立于C28x CPU工作,时钟频率与CPU相同,可执行算法以及周期性的计算工作。通过增加平行的处理单元CLA,拓展了C28x CPU的性能。

典型应用

电机控制示例如下:

void PWMA_config(void)

{P_SW2 |= 0x80; //SFR enable PWM1 = 0;PWM1_L = 0;PWM2 = 0;PWM2_L = 0;PWM3 = 0;PWM3_L = 0;P1n_push_pull(0x3f);PWMA_PSCR = 3; // 预分频寄存器, 分频 Fck_cnt = Fck_psc/(PSCR[15:0}+1), 边沿对齐PWM频率 = SYSclk/((PSCR+1)*(AAR+1)), 中央对齐PWM频率 = SYSclk/((PSCR+1)*(AAR+1)*2).PWMA_DTR = 24; // 死区时间配置, n=0~127: DTR= n T, 0x80 ~(0x80+n), n=0~63: DTR=(64+n)*2T, // 0xc0 ~(0xc0+n), n=0~31: DTR=(32+n)*8T, 0xE0 ~(0xE0+n), n=0~31: DTR=(32+n)*16T,PWMA_ARR = 255; // 自动重装载寄存器, 控制PWM周期PWMA_CCER1 = 0;PWMA_CCER2 = 0;PWMA_SR1 = 0;PWMA_SR2 = 0;PWMA_ENO = 0;PWMA_PS = 0;PWMA_IER = 0;PWMA_CCMR1 = 0x68; // 通道模式配置, PWM模式1, 预装载允许PWMA_CCR1 = 0; // 比较值, 控制占空比(高电平时钟数)PWMA_CCER1 |= 0x05; // 开启比较输出, 高电平有效PWMA_PS |= 0; // 选择IO, 0:选择P1.0 P1.1, 1:选择P2.0 P2.1, 2:选择P6.0 P6.1,

bit4: ENO3P, bit3: ENO2N, bit2: ENO2P, bit1: ENO1N, bit0: ENO1PPWMA_CCMR2 = 0x68; // 通道模式配置, PWM模式1, 预装载允许PWMA_CCR2 = 0; // 比较值, 控制占空比(高电平时钟数)PWMA_CCER1 |= 0x50; // 开启比较输出, 高电平有效PWMA_PS |= (0<<2); // 选择IO, 0:选择P1.2 P1.3, 1:选择P2.2 P2.3, 2:选择P6.2 P6.3,

bit4: ENO3P, bit3: ENO2N, bit2: ENO2P, bit1: ENO1N, bit0: ENO1PPWMA_CCMR3 = 0x68; // 通道模式配置, PWM模式1, 预装载允许PWMA_CCR3 = 0; // 比较值, 控制占空比(高电平时钟数)PWMA_CCER2 |= 0x05; // 开启比较输出, 高电平有效PWMA_PS |= (0<<4); // 选择IO, 0:选择P1.4 P1.5, 1:选择P2.4 P2.5, 2:选择P6.4 P6.5, PWMA_BKR = 0x80; // 主输出使能 相当于总开关PWMA_CR1 = 0x81; // 使能计数器, 允许自动重装载寄存器缓冲, 边沿对齐模式, 向上计数, bit7=1:写自动重装载寄存器缓冲(本周期不会被打扰), =0:直接写自动重装载寄存器本(周期可能会乱掉)PWMA_EGR = 0x01; //产生一次更新事件, 清除计数器和与分频计数器, 装载预分频寄存器的值

}void StepMotor(void)

{switch(step){case 0: // AB PWM1, PWM2_L=1PWMA_ENO = 0x00; PWM1_L=0; PWM3_L=0;Delay_500ns();PWMA_ENO = 0x01; // 打开A相的高端PWMPWM2_L = 1; // 打开B相的低端ADC_CONTR = 0x80+10; // 选择P0.2作为ADC输入 即C相电压CMPCR1 = 0x8c + 0x10; //比较器下降沿中断break;case 1: // AC PWM1, PWM3_L=1PWMA_ENO = 0x01; PWM1_L=0; PWM2_L=0; // 打开A相的高端PWMDelay_500ns();PWM3_L = 1; // 打开C相的低端ADC_CONTR = 0x80+9; // 选择P0.1作为ADC输入 即B相电压CMPCR1 = 0x8c + 0x20; //比较器上升沿中断break;case 2: // BC PWM2, PWM3_L=1PWMA_ENO = 0x00; PWM1_L=0; PWM2_L=0;Delay_500ns();PWMA_ENO = 0x04; // 打开B相的高端PWMPWM3_L = 1; // 打开C相的低端ADC_CONTR = 0x80+8; // 选择P0.0作为ADC输入 即A相电压CMPCR1 = 0x8c + 0x10; //比较器下降沿中断break;case 3: // BA PWM2, PWM1_L=1PWMA_ENO = 0x04; PWM2_L=0; PWM3_L=0; // 打开B相的高端PWMDelay_500ns();PWM1_L = 1; // 打开C相的低端ADC_CONTR = 0x80+10; // 选择P0.2作为ADC输入 即C相电压CMPCR1 = 0x8c + 0x20; //比较器上升沿中断break;case 4: // CA PWM3, PWM1_L=1PWMA_ENO = 0x00; PWM2_L=0; PWM3_L=0;Delay_500ns();PWMA_ENO = 0x10; // 打开C相的高端PWMPWM1_L = 1; // 打开A相的低端adc11 = ((adc11 *7)>>3) + Get_ADC10bitResult(11);ADC_CONTR = 0x80+9; // 选择P0.1作为ADC输入 即B相电压CMPCR1 = 0x8c + 0x10; //比较器下降沿中断break;case 5: // CB PWM3, PWM2_L=1PWMA_ENO = 0x10; PWM1_L=0; PWM3_L=0; // 打开C相的高端PWMDelay_500ns();PWM2_L = 1; // 打开B相的低端ADC_CONTR = 0x80+8; // 选择P0.0作为ADC输入 即A相电压CMPCR1 = 0x8c + 0x20; //比较器上升沿中断break;default:break;}if(B_start) CMPCR1 = 0x8C; // 启动时禁止下降沿和上升沿中断

}开发工具链

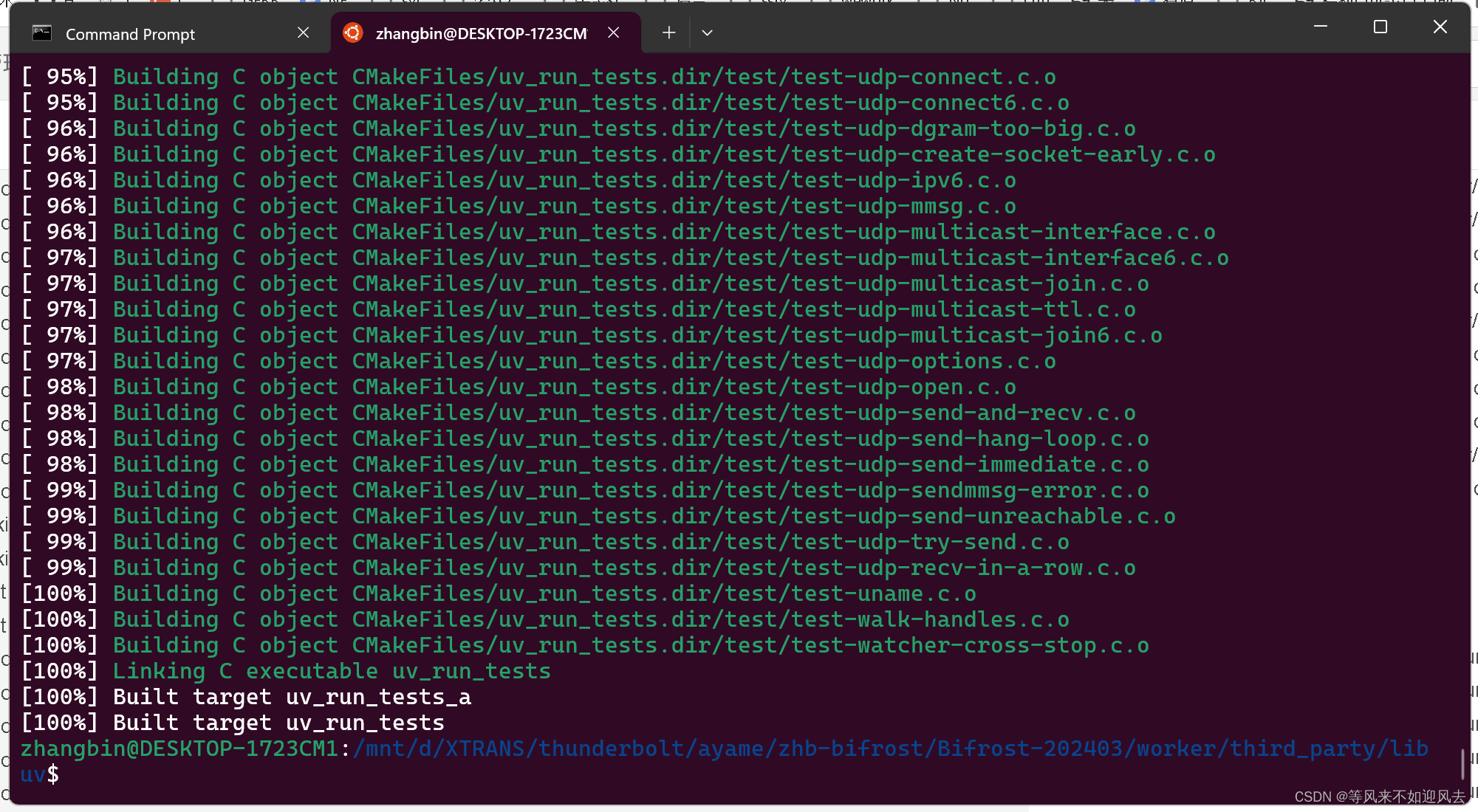

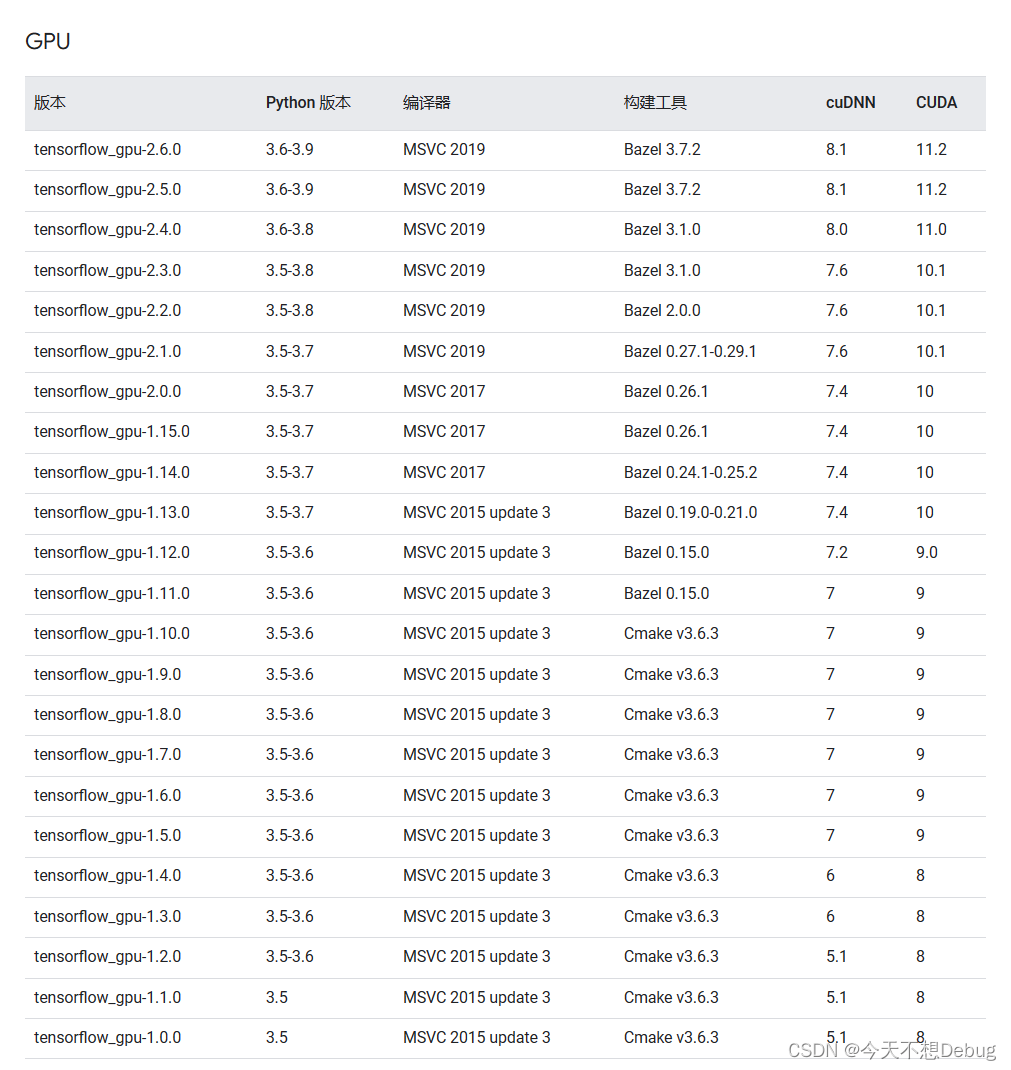

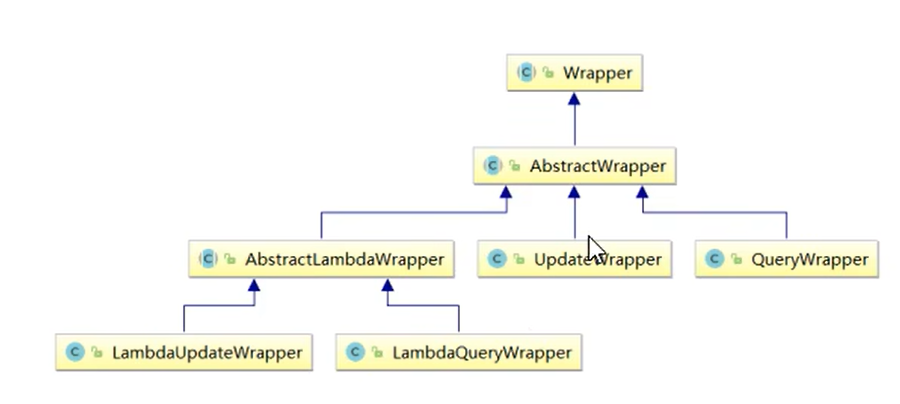

底层软件库、软件demo、工具链,示例如下:

参考资料

TMS320F28003x Real-Time Microcontrollers datasheet.pdf