本节目录

一、设计背景

二、设计思路

三、逻辑设计框架

四、仿真验证

五、上板验证

六、往期文章链接

本节内容

一、设计背景

通常,芯片手册或者IP都会提供一系列的用户寄存器以及相关的定义,用于软件开发人员进行控制底层硬件来调试,或封装API提供给用户侧使用。相同的设计思路,也适用于FPGA开发,在FPGA内部自定义一系列的寄存器,包括:业务寄存器和调试寄存器等等。好处有两个方面,一方面方便FPGA工程师用来调试,定位bug,优化修改代码;二是可以灵活的开发给软件,由软件人员根据寄存器的手册进行二次封装,从而实现客户的各类需求。当然,若因为新增客户需求而不断修改调试FPGA代码,是否考虑前期设计的代码的兼容性,可以通过寄存器方式支持不同功能需求的切换,从而满足客户的应用场景。

二、设计思路

那么如何从串口实现FPGA内部寄存器的控制?

设计的想法,灵感来源于内部AXILITE总线,一种轻量级的寄存器读写访问总线,总线通过五个通道实现内部axilite寄存器的读写控制。

串口内容如何与AXILITE的五个通道进行一一映射?

用过AXILITE总线的FPGA开发者,或多或少都了解这个总线信号五个通道,相当多,也有直接逻辑控制各个通道的信号,而此处的思路是引入wishbone总线,通过控制wishbone总线的读写,借助于成熟开源的wishbone总线转换AXI总线的模块,从而实现axilite寄存器的读写控制。

三、逻辑设计框架

工程源码中vivado版本为2022.2,仿真采用Modelsim2020.4,当然用vivado自带的也可以进行仿真验证。

设计框架中,通过宏定义实现两套代码的仿真验证以及上板,需要对应修改xdc的管脚约束。①是frame实现axilite寄存器的读写控制;②是loop的fifo环回测试。

uart_frame代码:内部自定义AXILITE寄存器,包括只读寄存器、可读可写寄存器的定义。在uart_frame_ctrl中,当PC电脑端发送寄存器写数据帧时,解析来自串口的数据,生成wishbone的写控制,完成axilite的寄存器的写入操作,同时,将接收的数据组帧后,并发送至PC串口显示。当PC电脑端发送寄存器读数据帧时,解析来自串口的数据,生成wishbone的读控制,完成axilite的寄存器的读取操作,同时,将读取的数据组帧后,并发送至PC串口显示。

uart_loop代码,上篇文章已经描述了具体的实现细节,此处就不过多描述了。

四、仿真验证

在testbench文件中,通过组帧实现固定数据帧的发送,从而实现fpga内部寄存器的读写控制,包括:读FPGA的版本号,读写测试寄存器以及通过控制led寄存器修改led的状态。

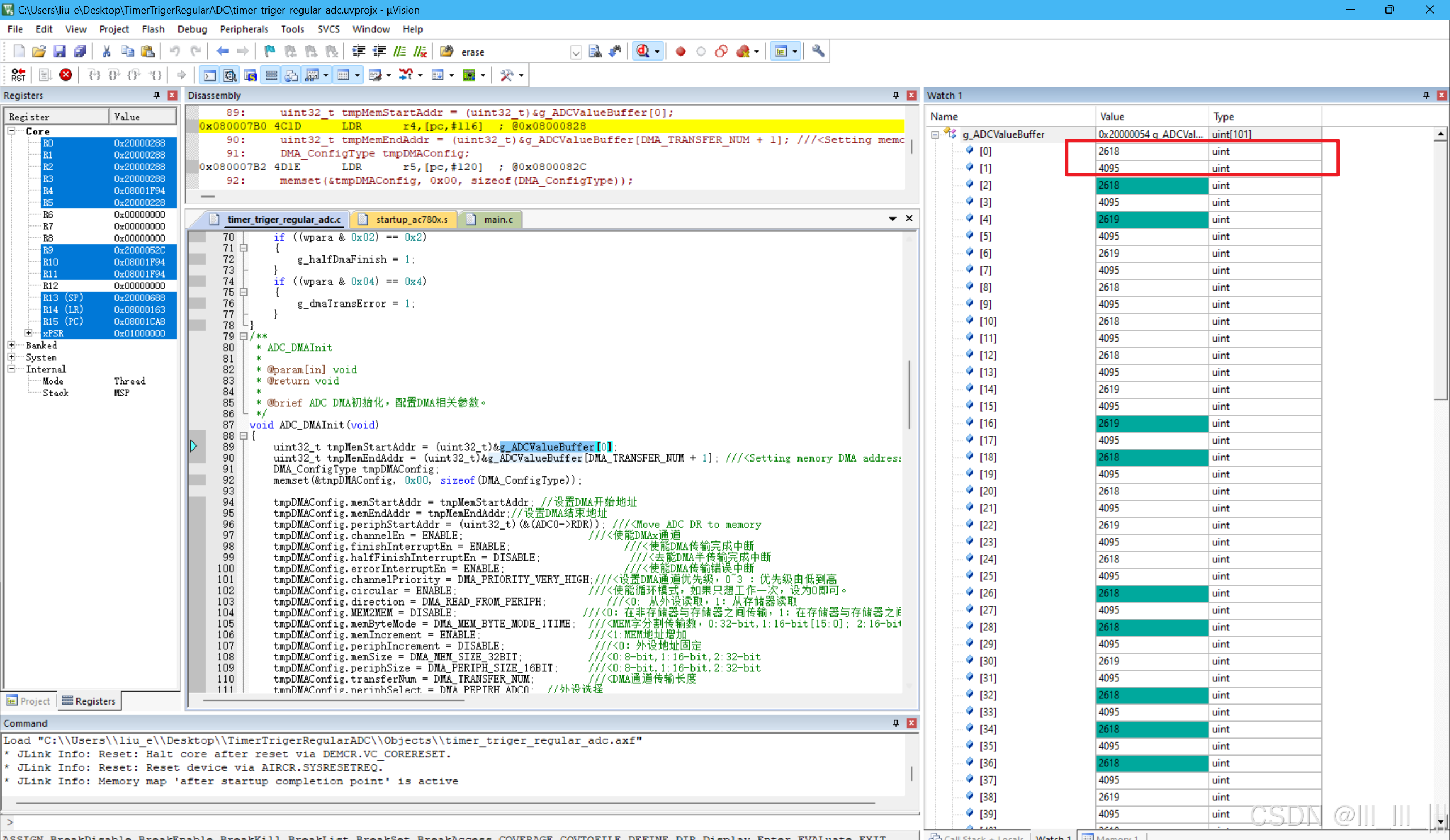

五、上板验证

//读版本寄存器32’h80000000

//A1B2C3D4800000000000000000000001A6B7C8D9

//写测试寄存器32’h80000004

//A1B2C3D4800000046666666600000001A6B7C8D9

//读测试寄存器32’h80000004

//A1B2C3D4800000040000000000000000A6B7C8D9

六、往期文章链接

UltraScale+FPGA中Serdes的多lane对齐异常解决方案

vivado时序报告中slack是如何计算的?如何优化时序?

UltraScale+FPGA中GTY的TX路径时钟详解——以40G的ETH MAC IP为例

vivado时序优化——约束异步时钟组set_clock_groups

基于FDMA和AXI4接口的DDR4遍历读写测试

基于fpga的图像处理之3x3_5x5算子模板设计

基于fpga的图像处理之3x3_5x5算子模板中值排序

基于fpga的图像处理之图像灰度化处理(Vivado+Modelsim+Matlab联合仿真验证)

AXI协议之AXILite开发设计(一)

AXI协议之AXILite开发设计(二)

AXI协议之AXILite开发设计(三)

AXI协议之AXILite开发设计(四)

AXI协议之AXILite开发设计(五)

FPGA和Matlab的FFT功能验证(一)

FPGA和Matlab的FFT功能验证(二)

FPGA和Matlab的FFT功能验证(三)

跟小灰灰一起学vivado:7系列FPGA的MultiBoot和Fallback功能更新固件

跟小灰灰一起学vivado:7系列FPGA配置模式之配置数据文件格式和配置时序步骤

跟小灰灰一起学vivado:7系列FPGA配置模式之主SPI四路(x4)

跟小灰灰一起学vivado:PCIe XDMA实现远程更新FPGA固件

Xilinx UltraScale+DDR4项目开发(一)——DDR4 MIG的ip接口信号

Xilinx UltraScale+DDR4项目开发(二)——DDR4 MIG的时钟网络

Xilinx UltraScale+DDR4项目开发(三)——DDR4器件选型与MIG IP的配置

低速接口项目之串口Uart开发(一)——串口UART

低速接口项目之串口Uart开发(二)——FIFO实现串口数据的收发回环测试

低速接口项目之串口Uart开发(三)——串口发送模块和接收模块

低速接口项目之串口Uart开发(四)——UART串口实现FPGA内部AXILITE寄存器的读写控制

低速接口项目之串口Uart开发(五)——QT实现Uart串口寄存器读写工具

低速接口项目之串口Uart开发(六)——zynq系列ps-pl端uart实现共享Axilite内部寄存器的读写

低速接口项目之串口Uart开发(七)——如何在FPGA项目中实现自适应波特率串口功能

低速接口项目之串口Uart开发(八)——如何通过ps侧的串口实现zynq的在线升级(一)

低速接口项目之串口Uart开发(九)——如何通过ps侧的串口实现zynq的在线升级(二)

低速接口项目之串口Uart开发(十)——基于EMIO的自定义PL串口实现zynq的在线升级